High-speed fixed point fast fourier transformation (FFT) processor based on field programmable gate array (FPGA) and processing method for high-speed fixed point FFT processor

A processor and high-speed technology, applied in the direction of complex mathematical operations, etc., can solve the problems of FFT processor control logic complexity, low operating frequency, long processing delay, etc., to achieve improved operating frequency and data processing speed, short design cycle, hardware high cost effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] The FFT processor of the present invention will be further described below in conjunction with the accompanying drawings.

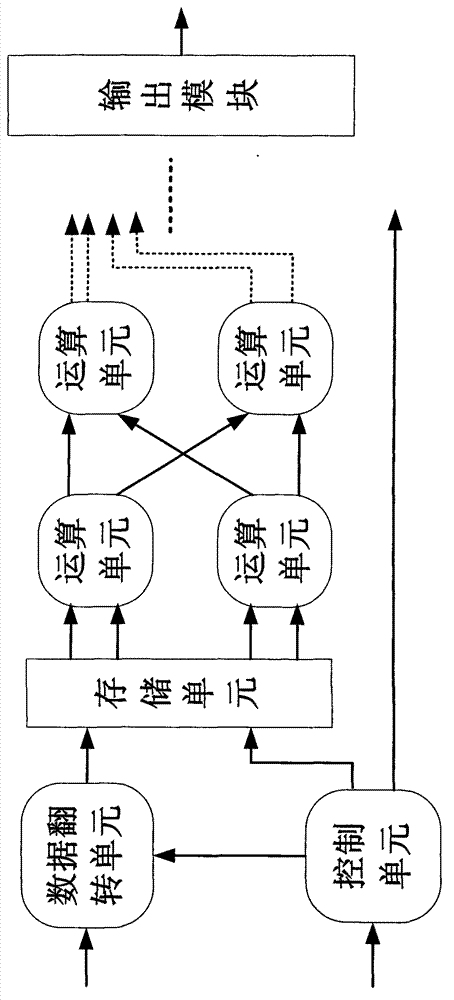

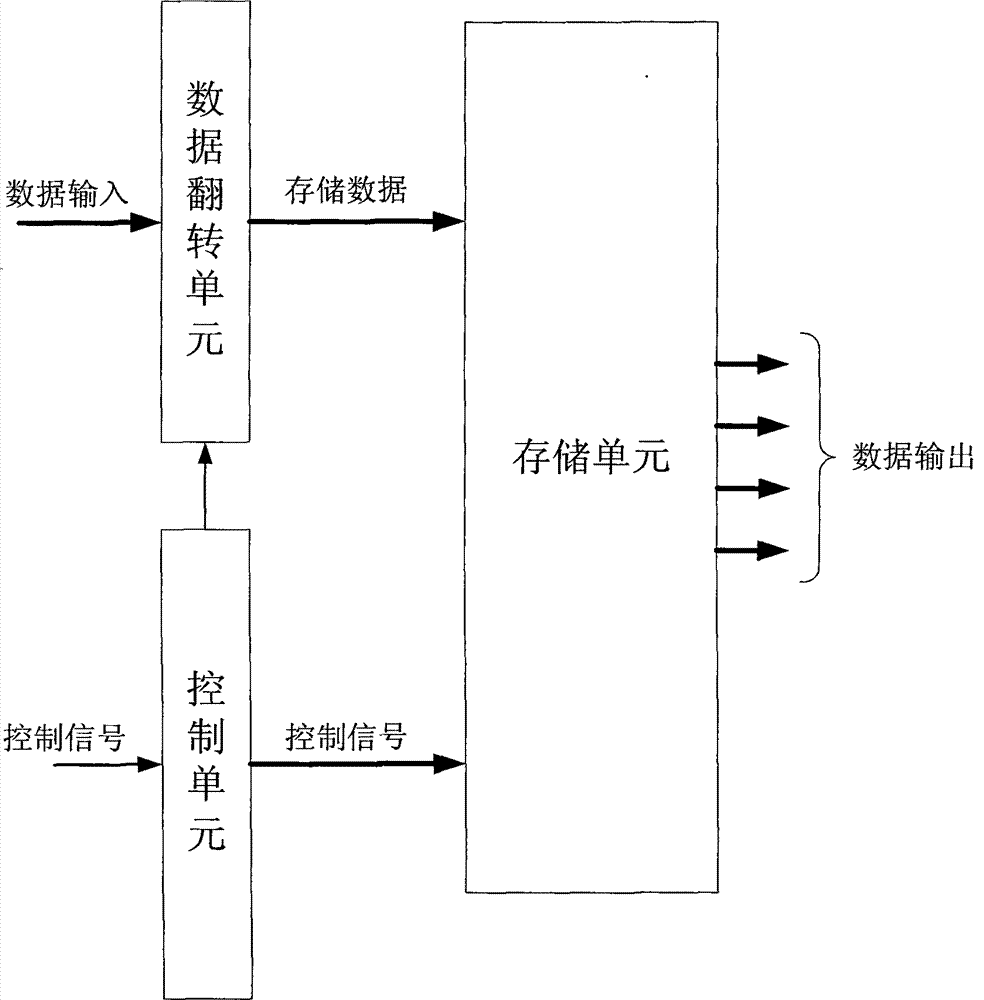

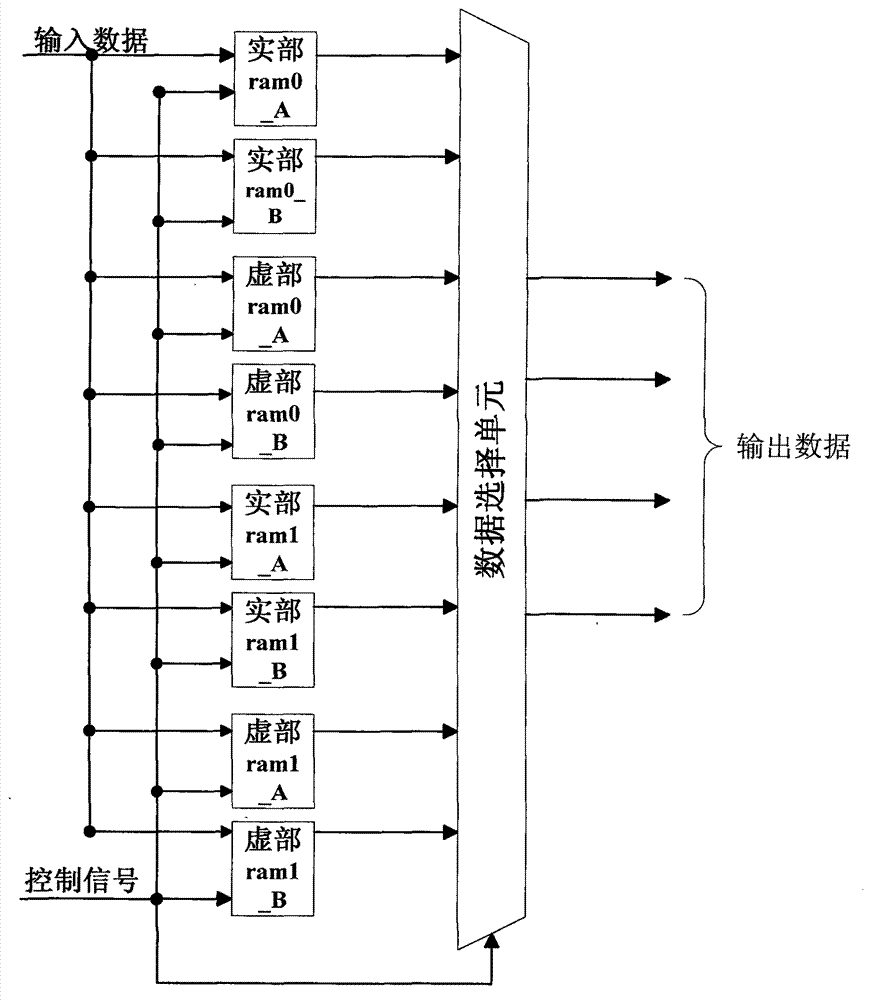

[0041] Refer to attached figure 1, the FFT processor of the present invention includes a multi-level FFT processing module and a first-level inversion sequence output module. The FFT processing module and the inversion sequence output module are cascaded through the data bus and the control bus according to the pipeline mode, and the cascading number of the multi-stage FFT processing modules is determined by the length of the data sequence processed by the FFT processor. In this embodiment, the FFT processing module The number of cascades is 10. The FFT processing module receives the input data from the previous FFT processing module or the FFT operation, performs butterfly processing on the input data, performs two butterfly processing on four corresponding data in each clock cycle, and outputs the processing results to A next-level FFT processi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More