An electro-static discharge protection circuit for an integrated circuit and a manufacturing method thereof

An electrostatic discharge and circuit protection technology, which is applied in the direction of circuits, electrical components, and electric solid devices, can solve problems such as premature aging of devices, reduced service life of integrated circuits, and damage, so as to prolong service life, improve utilization rate, reduce small size effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the accompanying drawings and examples.

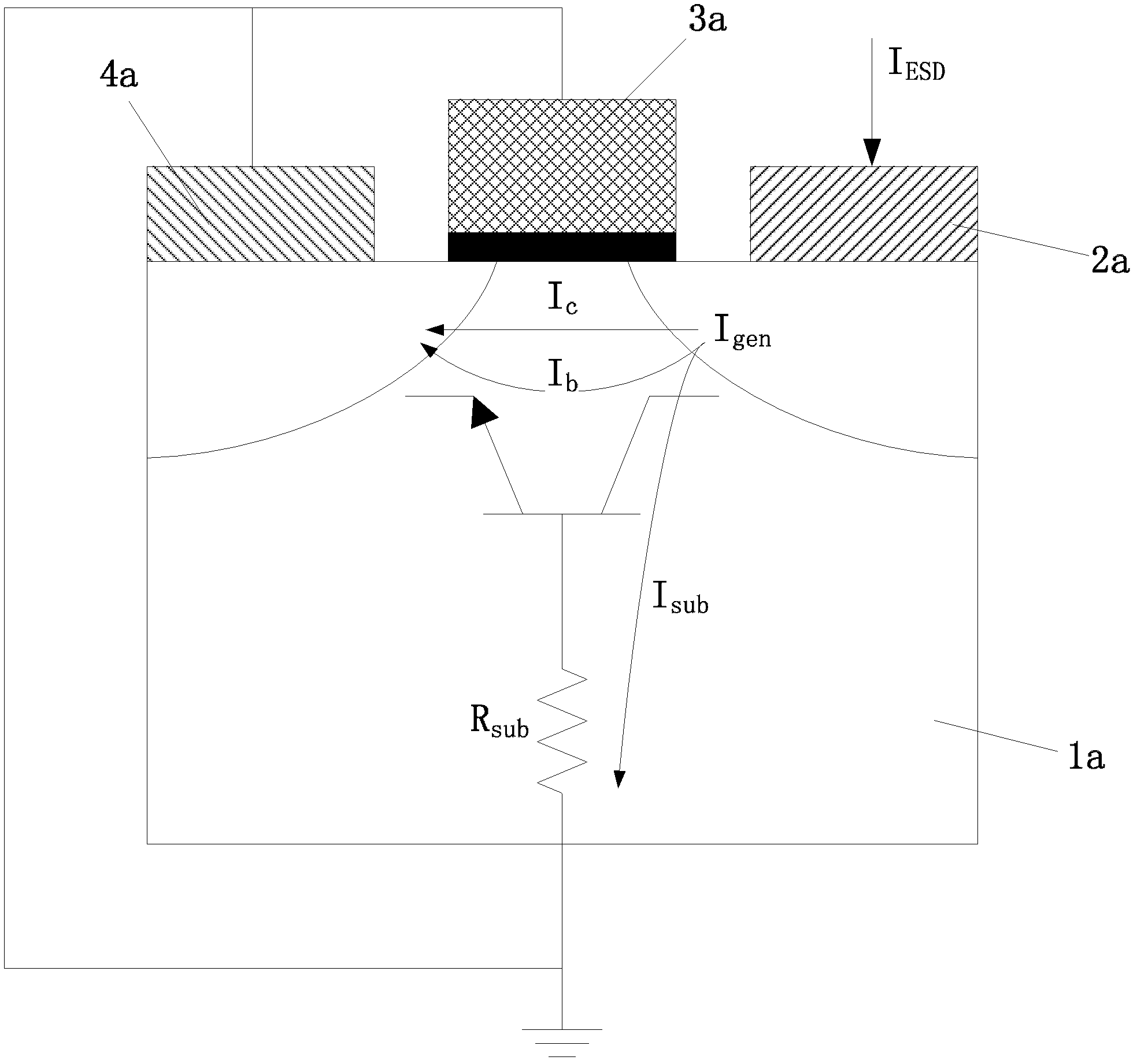

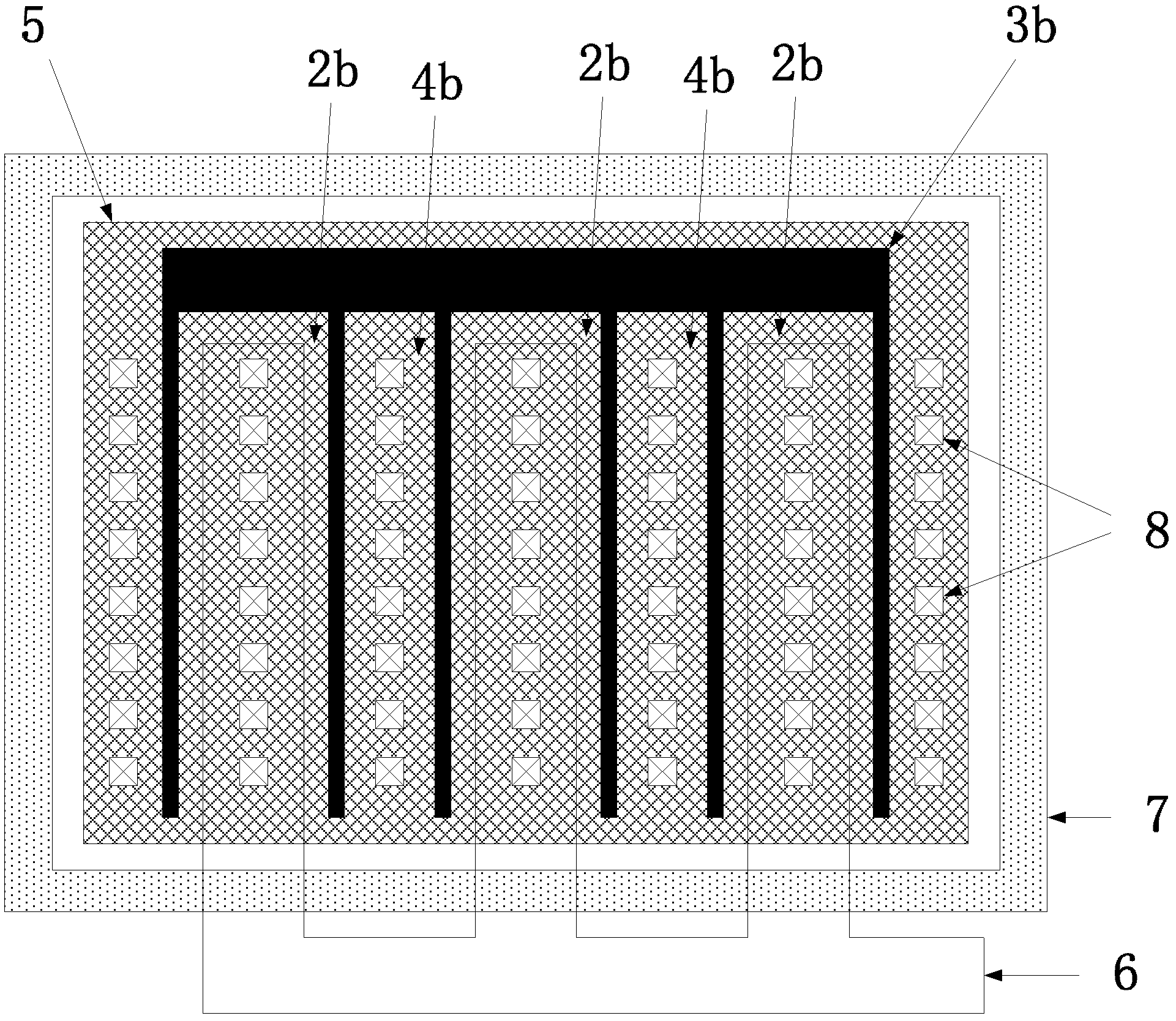

[0030] As a specific embodiment, the integrated circuit electrostatic discharge protection circuit structure of the present invention is as follows Figure 5shown. Without changing the size of the pick-up region 7 in the prior art, the length and width dimensions of the GGNMOS are reduced, that is, the length and width dimensions of the source and drain regions 5 are reduced, and the substrate between the source and drain regions 5 and the pick-up region 7 A plurality of through-silicon vias 9 (TSV, Through Silicon Via) are formed in it. Specifically, the structure of the integrated circuit electrostatic discharge protection circuit of the present invention is as follows: a source and drain region 5 is formed on the substrate, and the size of the sourc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More