Method For Solidifying A Semiconductor With Adding Charges Of A Doped Semiconductor During The Crystallisation

A curing method and semiconductor technology, applied in semiconductor devices, chemical instruments and methods, crystal growth, etc., can solve problems such as non-uniform resistivity, resistivity reduction, and severe

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0075] Below in conjunction with specific embodiment, further set forth the present invention:

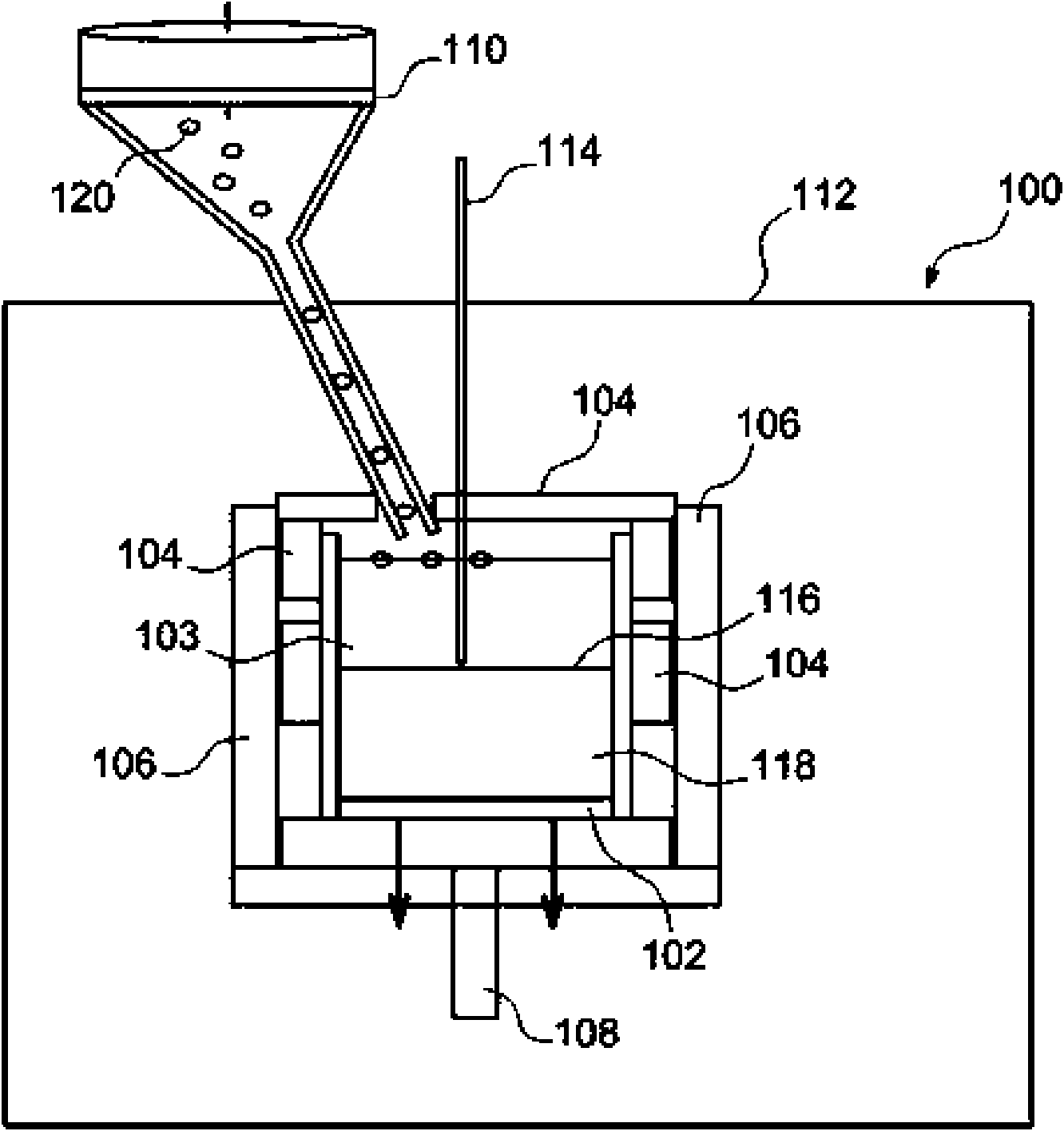

[0076] Such as figure 1 As shown, the figure shows a crystal growth Bridgman drop furnace 100, or zone melting oven, in which a semiconductor solidification process, in this example a crystallization operation, is performed.

[0077] The oven 100 includes a crucible 102 designed to hold molten semiconductor 103 to be crystallized. exist figure 1 In this crucible 102 a crystallized semiconductor 118 is obtained, ie located below the immersion bath in which the semiconductor 103 is melted. The oven 100 also contains heating means 104 , which are, for example electrically supplied, arranged above the crucible 102 and rest at the upper part of the side walls of the crucible 102 . The heating elements 104 are used to melt the semiconductor as it is introduced into the crucible 102 in solid form and maintain it in a molten form. The oven 100 also includes an insulated side wall 106 ....

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More