Method for reducing random access memory (RAM) expense in abrasion balanced processing

A technology of wear leveling and overhead, applied in the direction of memory address/allocation/relocation, response error generation, redundant code error detection, etc., can solve problems such as large memory overhead, achieve memory reduction, reduce memory overhead, and improve The effect of operating speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

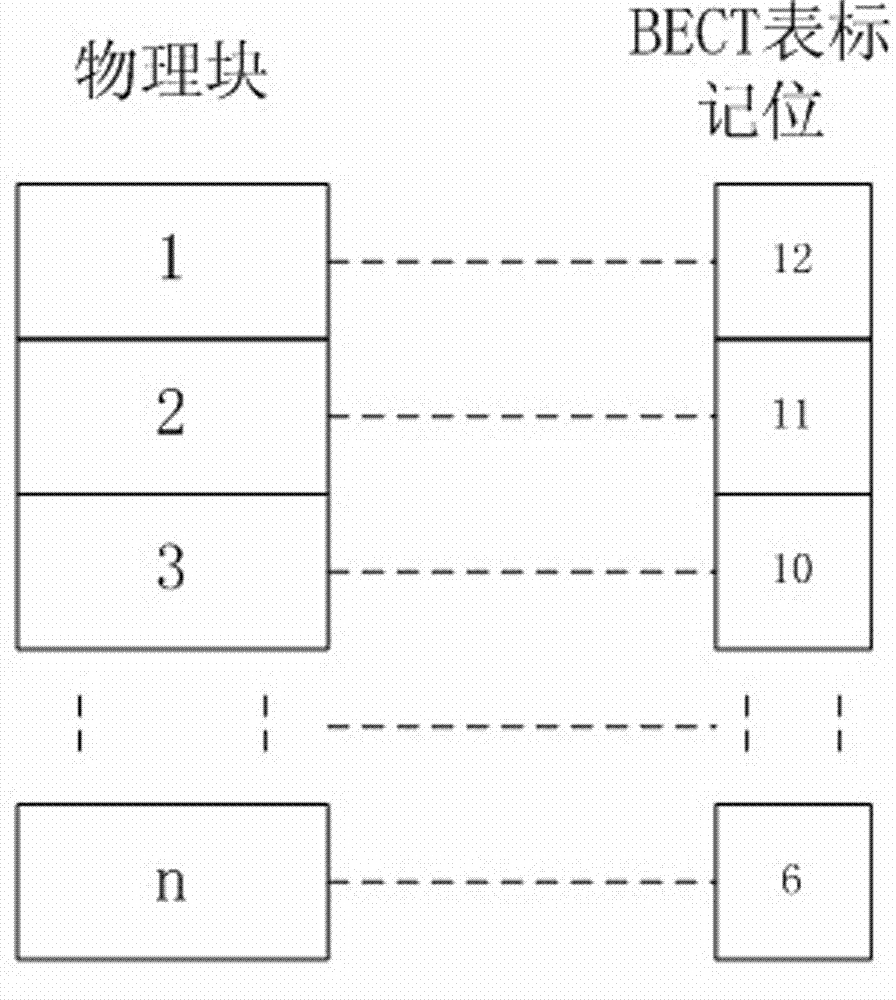

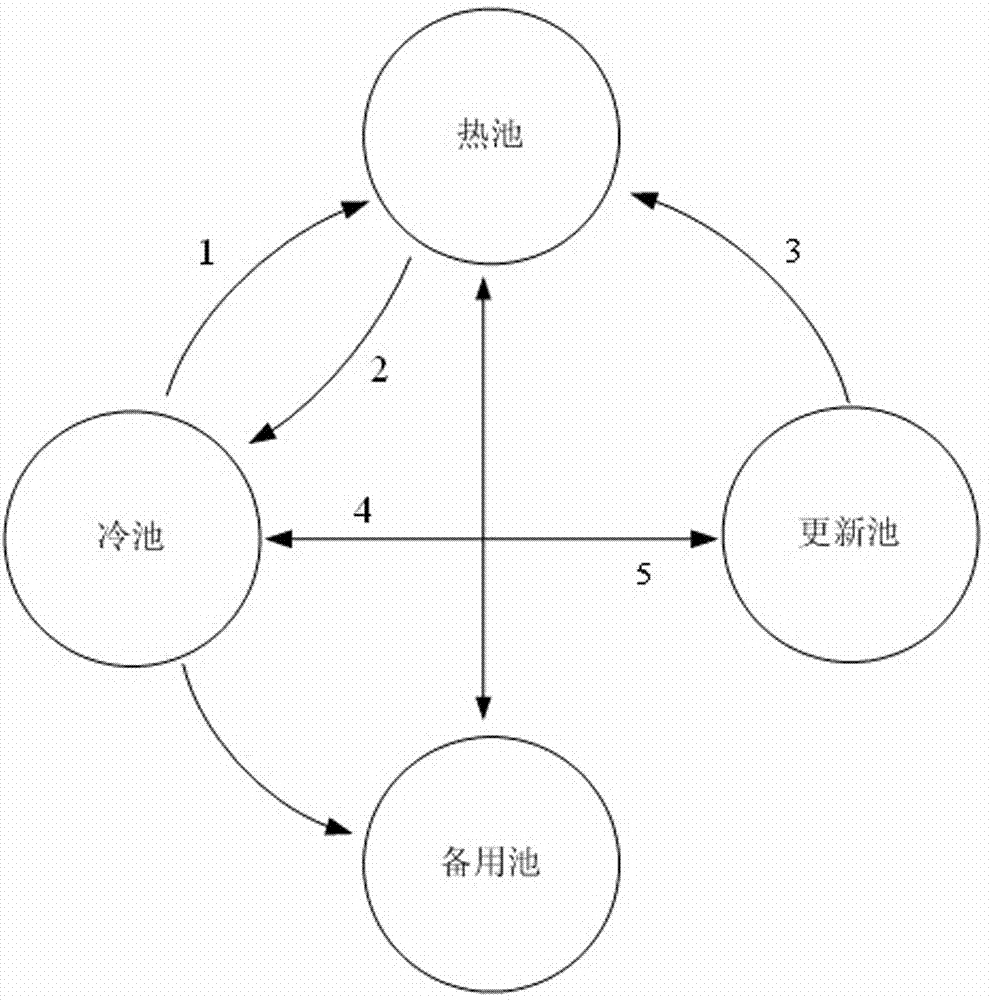

[0034] Based on the existing flash memory wear leveling algorithm, this paper proposes a method to reduce the memory overhead during wear leveling execution. When flash memory performs wear leveling, the main memory overhead is to load the wear leveling table. The table mainly has two data structures: physical block identifier and physical block erasure status. The method uses the number of error correction bits of the error correction code to replace the erasing times of the physical block, so that the memory occupied by the wear leveling table is greatly reduced.

[0035] It should be known that the current mainstream flash memory is non-flash memory, and of course there is also XOR (or non-flash memory). Obviously, in terms of data access alone, there will be steps for data error correction. Obviously, according to the main application objects of this article and non-flash memory The method for flash memory can also be applied to other types of flash memory.

[0036] The f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More