1.5t dynamic memory cell, array and operation method based on resistive switching gate dielectric

A technology of dynamic storage and cell array, applied in the field of memory, can solve problems such as poor compatibility of CMOS process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

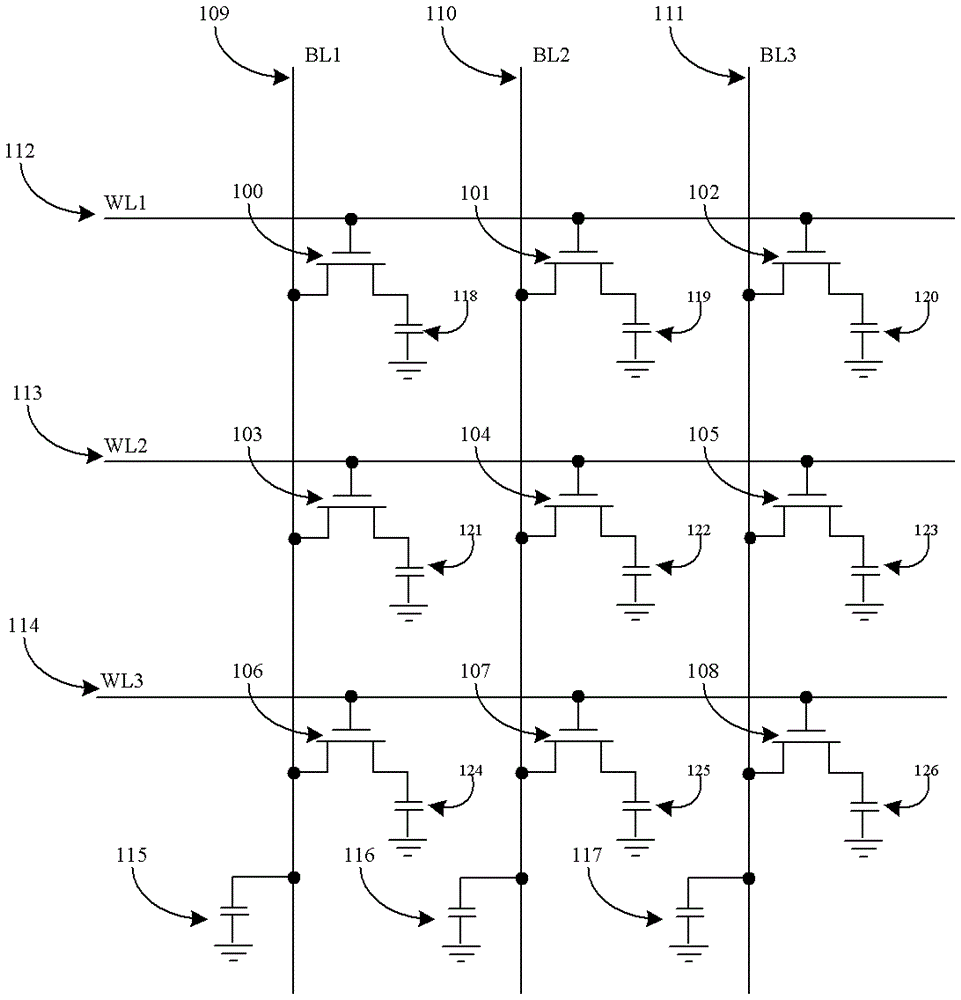

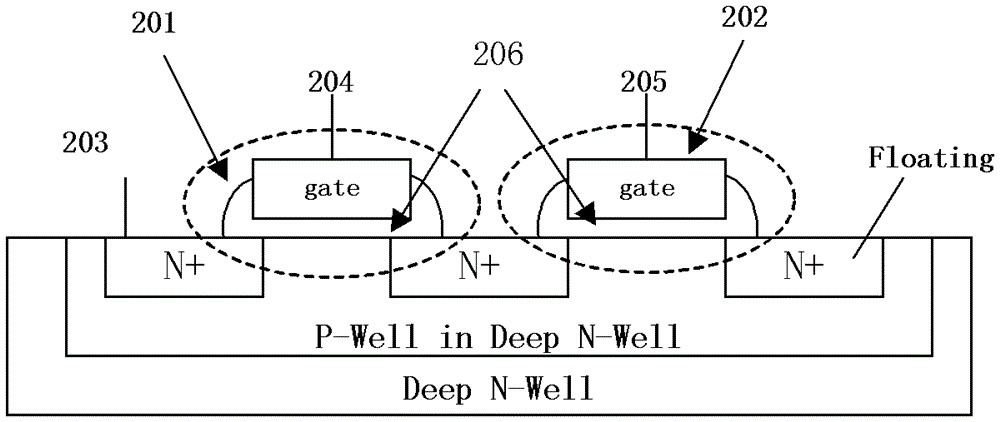

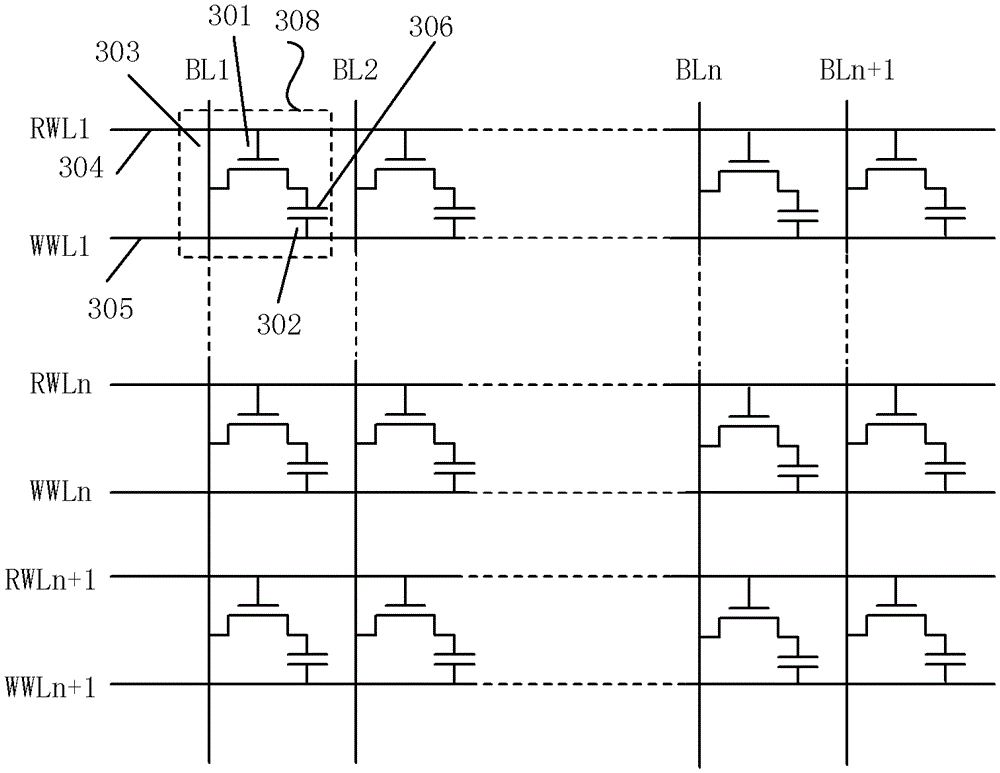

[0020] According to an embodiment of the present invention, the 1.5T dynamic memory cell and the array based on the resistive gate dielectric include: a transistor, including a source, a drain, and a control gate; a storage node, that is, the gate dielectric of the transistor control gate, located at the Between the control gate and the silicon substrate, the storage resistance changes; the word line is connected to the control gate of the transistor; the bit line is connected to the drain of the transistor; the source line is connected to the source of the transistor . Reference attached figure 2 , is a 1.5T dynamic memory cell based on a resistive gate medium according to an embodiment of the present invention, wherein 201 is named as a read tube, which plays the role of gating and current limiting, 202 is a programming component, 203 is a bit line, and 204 represents The word line 201 is the read word line, and 205 represents the programming word line. The gate 206 is ma...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com