2t dynamic memory cell and array structure based on resistive gate dielectric and its operation method

A technology of dynamic storage and array structure, applied in the field of memory, can solve the problems of physical or technological realization obstacles, difficulty in manufacturing large capacitance, etc., and achieve the effect of reducing refresh frequency and low power consumption application

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

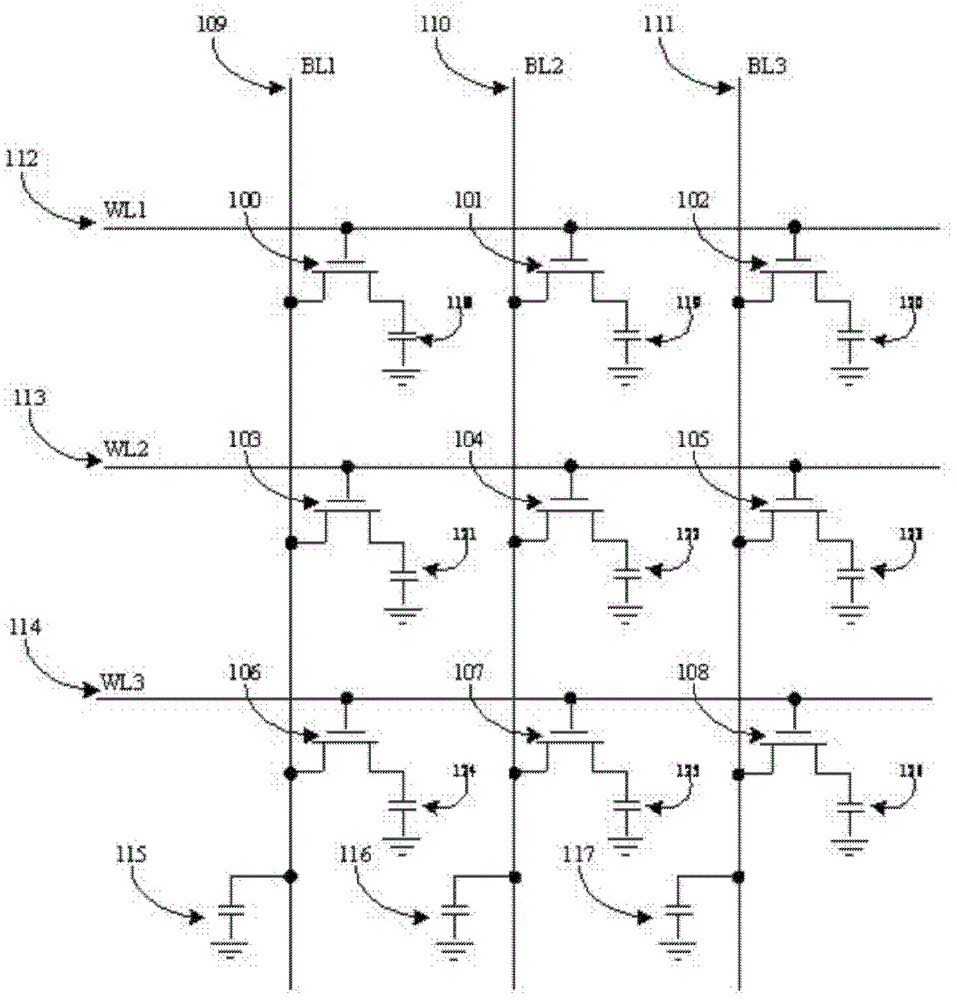

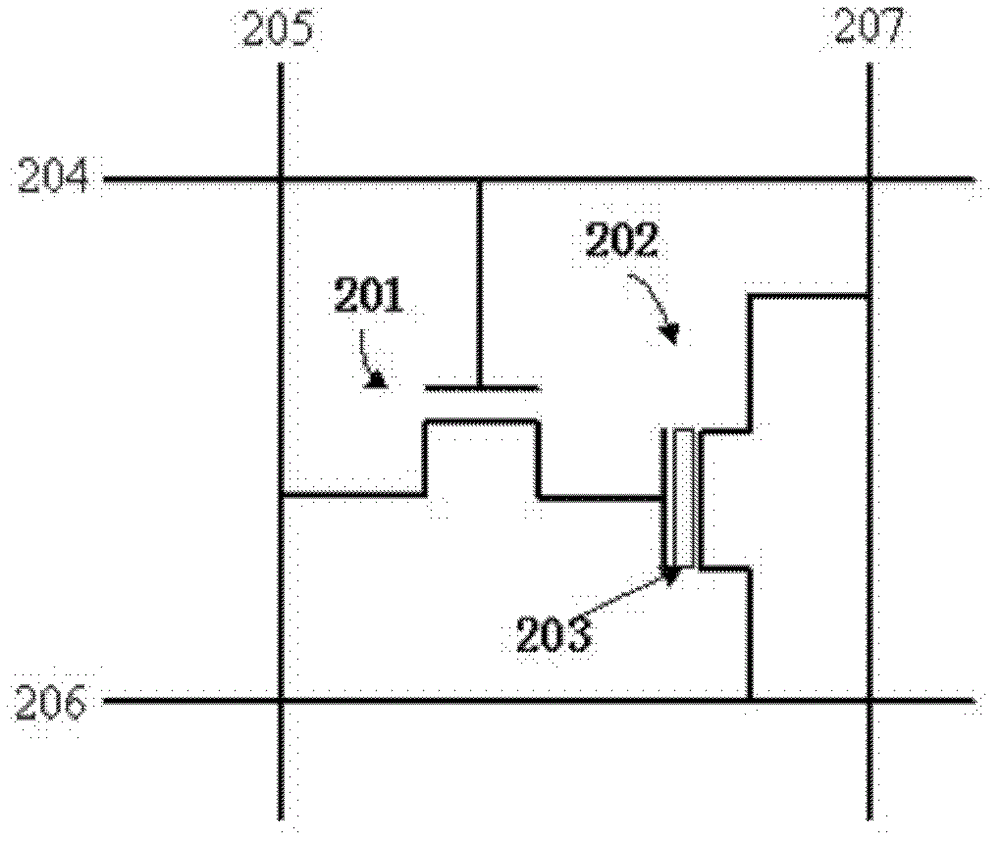

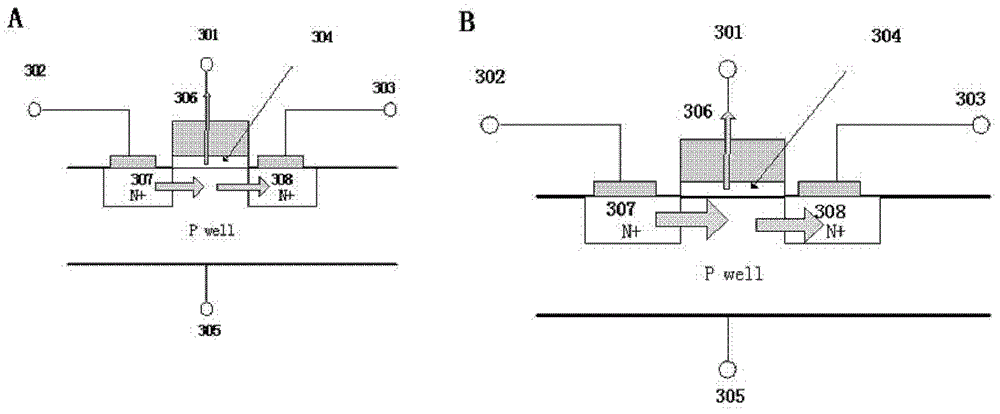

[0025] According to an embodiment of the present invention, a 2T dynamic memory cell and an array structure based on a resistive gate medium include a write tube 201, a read tube 202, a storage unit 203, a write word line (WWL) 204, and a write bit line (WBL) 205, Read word line (RWL) 206, read bit line (RBL) 207; the source end of write tube 201 is connected to the gate of read tube 202; write tube 201 has the function of programming; read the grid medium 203 of tube 202 It is a storage component; the 203 uses a resistive material, such as HfOx, which has three different states of insulation, high resistance, and low resistance, wherein the transition between high resistance and low resistance is reversible, and is transformed by SET and RESET voltages, respectively. The process from an insulated state to a high / low resistance is called FORMING; during programming, the write word line 204 is turned on, and the voltage added to the write bit line 205 end is transmitted to the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More