A parasitic n-i-p type pin device structure and manufacturing method in a bicmos process

An N-I-P, device structure technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as large insertion loss and limited forward conduction current capability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

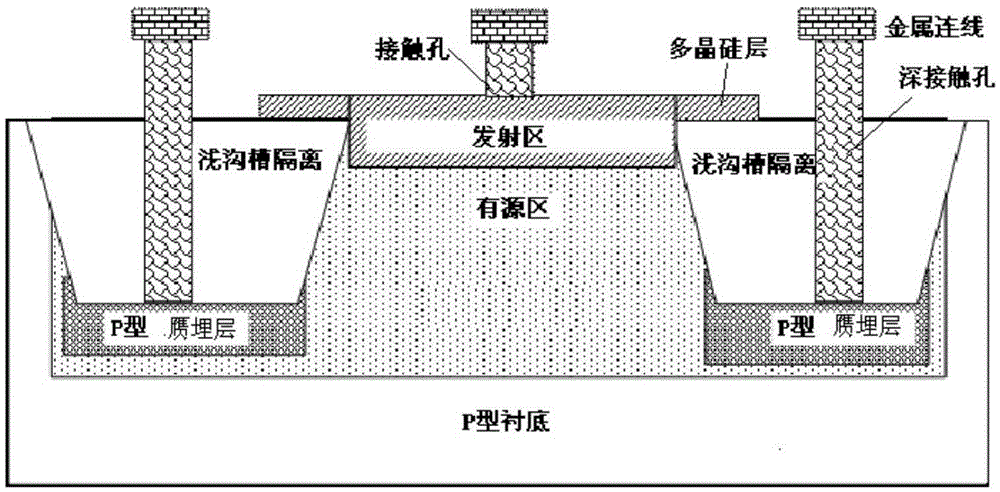

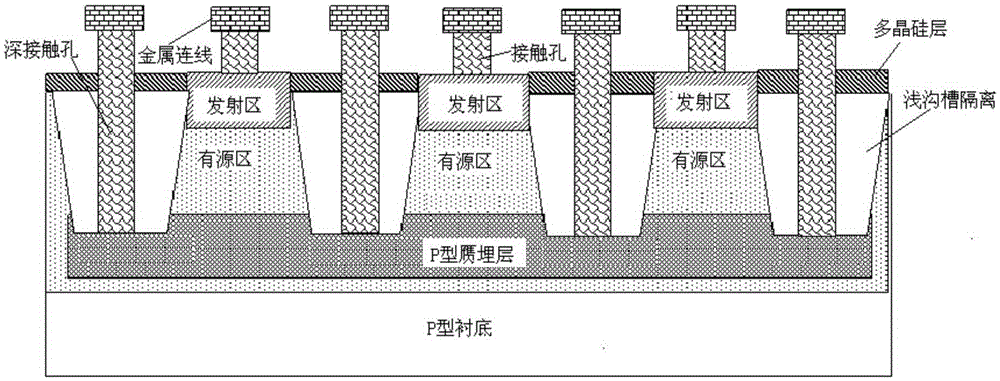

[0025] Such as figure 2 Shown, the parasitic N-I-P type PIN device structure of the present invention comprises:

[0026] An active region is formed above the P-type substrate, and a P-type pseudo-buried layer is formed in the active region. A plurality of shallow trench isolations are formed above the P-type pseudo-buried layer, and a polysilicon layer is formed on the shallow trench isolation. An emitter region is formed above the source region, and the emitter region and the polysilicon layer are alternately arranged. The emitter region is connected to a metal wire through a contact hole, and the P-type pseudo-buried layer is connected to a metal wire through a deep contact hole. The deep contact hole has titanium or tin and tungsten.

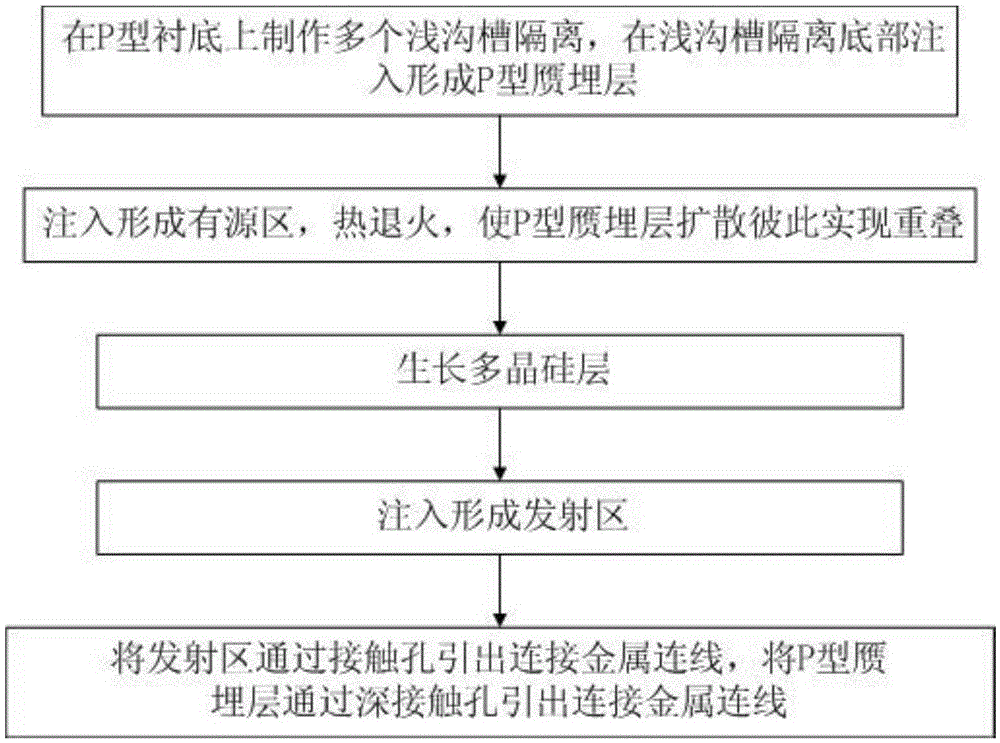

[0027] Such as image 3 Shown, the manufacturing method of parasitic N-I-P type PIN device structure of the present invention comprises:

[0028] (1) if Figure 4 As shown, a plurality of shallow trench isolations are made on a P-type s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More