A method of manufacturing a semiconductor packaging device

A technology for packaging devices and manufacturing methods, which is applied in the manufacture of semiconductor/solid-state devices, semiconductor devices, electric solid-state devices, etc., can solve the problem of lead frame and plastic packaging material pins or chip carriers falling off, low bonding strength between lead frame and plastic packaging material, The pins cannot complete the packaging process and other problems, so as to achieve the effects of low cost, prevention of delamination and high reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The present invention is described in detail below in conjunction with accompanying drawing:

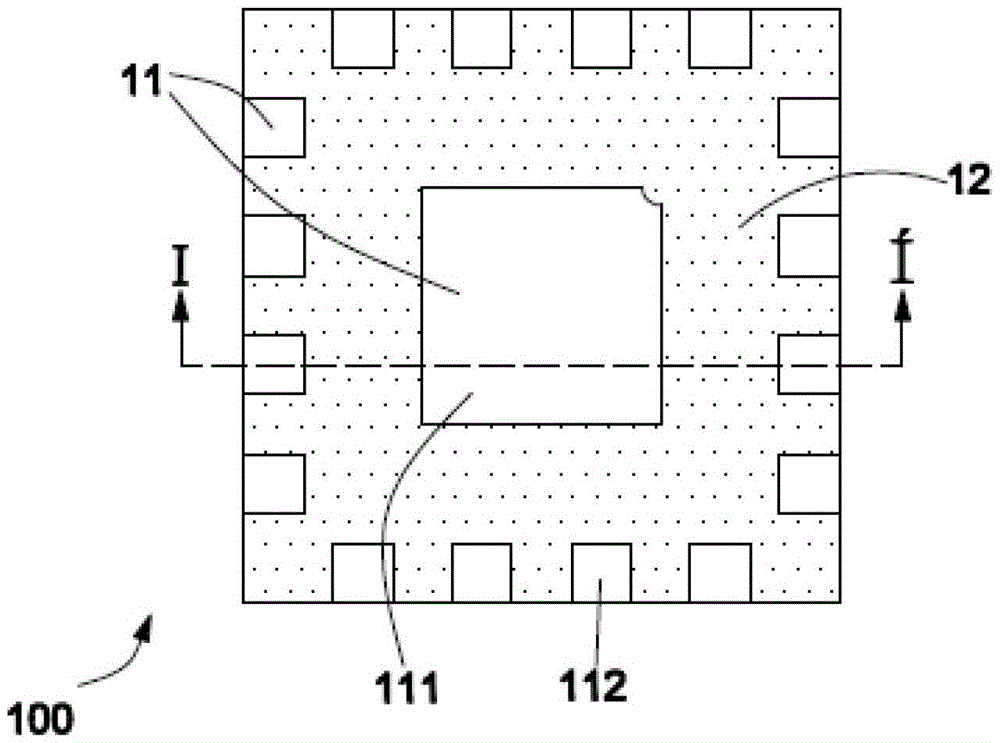

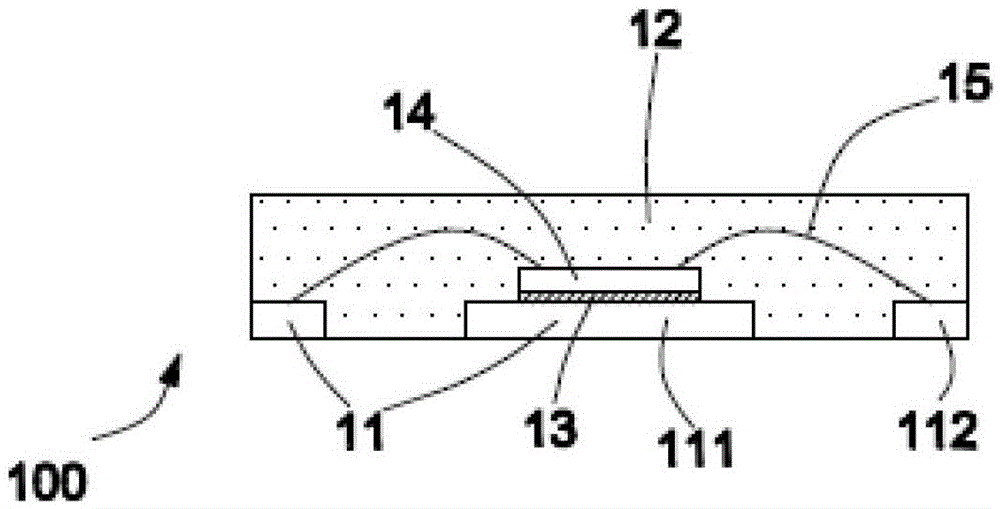

[0042] Figure 2A A schematic diagram of the back side of a QFN packaged device with a multi-circle pin arrangement in which the cross-section of the pins is circular and the pins on each side of the chip carrier are arranged in parallel according to the embodiment of the present invention.

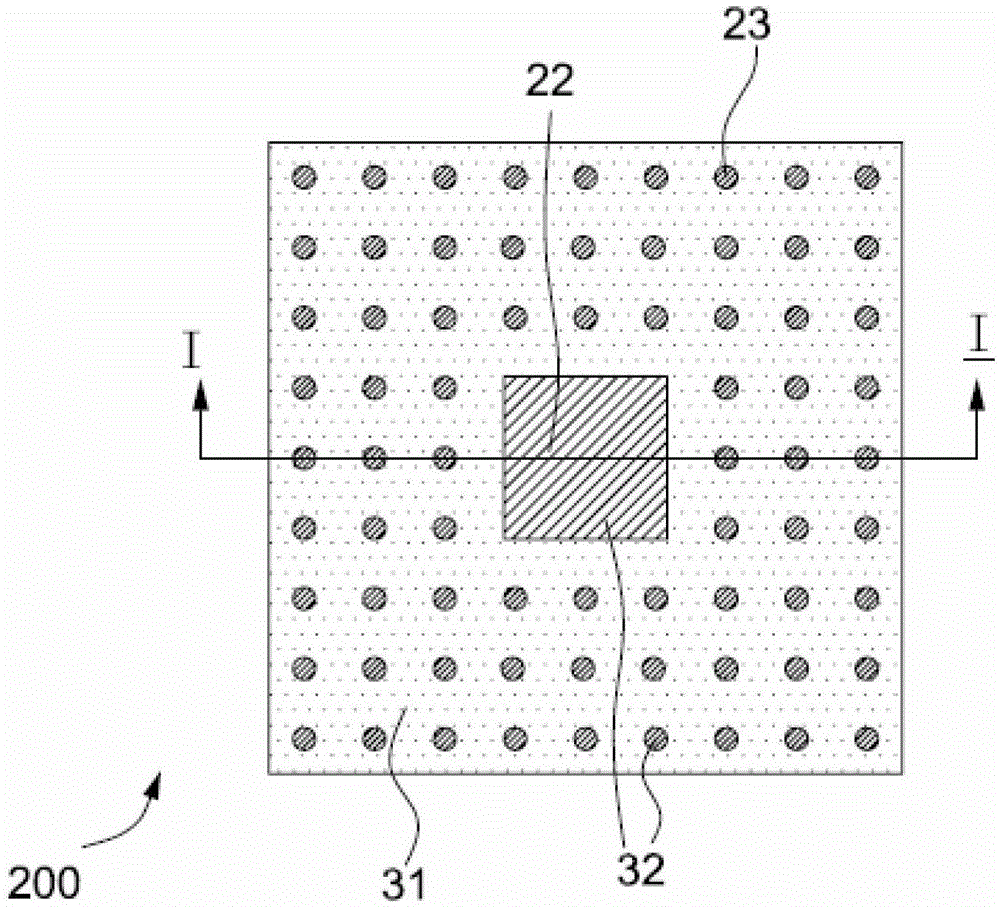

[0043] Refer to the above Figure 2A It can be seen that in this embodiment, the QFN packaged device 200 with multi-turn pin arrangement has a chip carrier 22 and pins 23 arranged in multi-turn around the chip carrier 22, and the arrangement of the pins 23 on each side of the chip carrier 22 The method is arranged in parallel, the cross section of the pins 23 is circular, the second metal material layer 32 is disposed on the surface of the chip carrier 22 and the pins 23 , and the plastic encapsulation material 31 is disposed in the QFN package device 200 . The arrangement of the pins 2...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More