Test component used in complementary metal-oxide-semiconductor transistor (CMOS) component and manufacture method and using method thereof

A technology for testing devices and devices, which is applied in the direction of single semiconductor device testing, semiconductor/solid-state device testing/measurement, semiconductor/solid-state device manufacturing, etc. Production cost, the effect of improving the yield rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

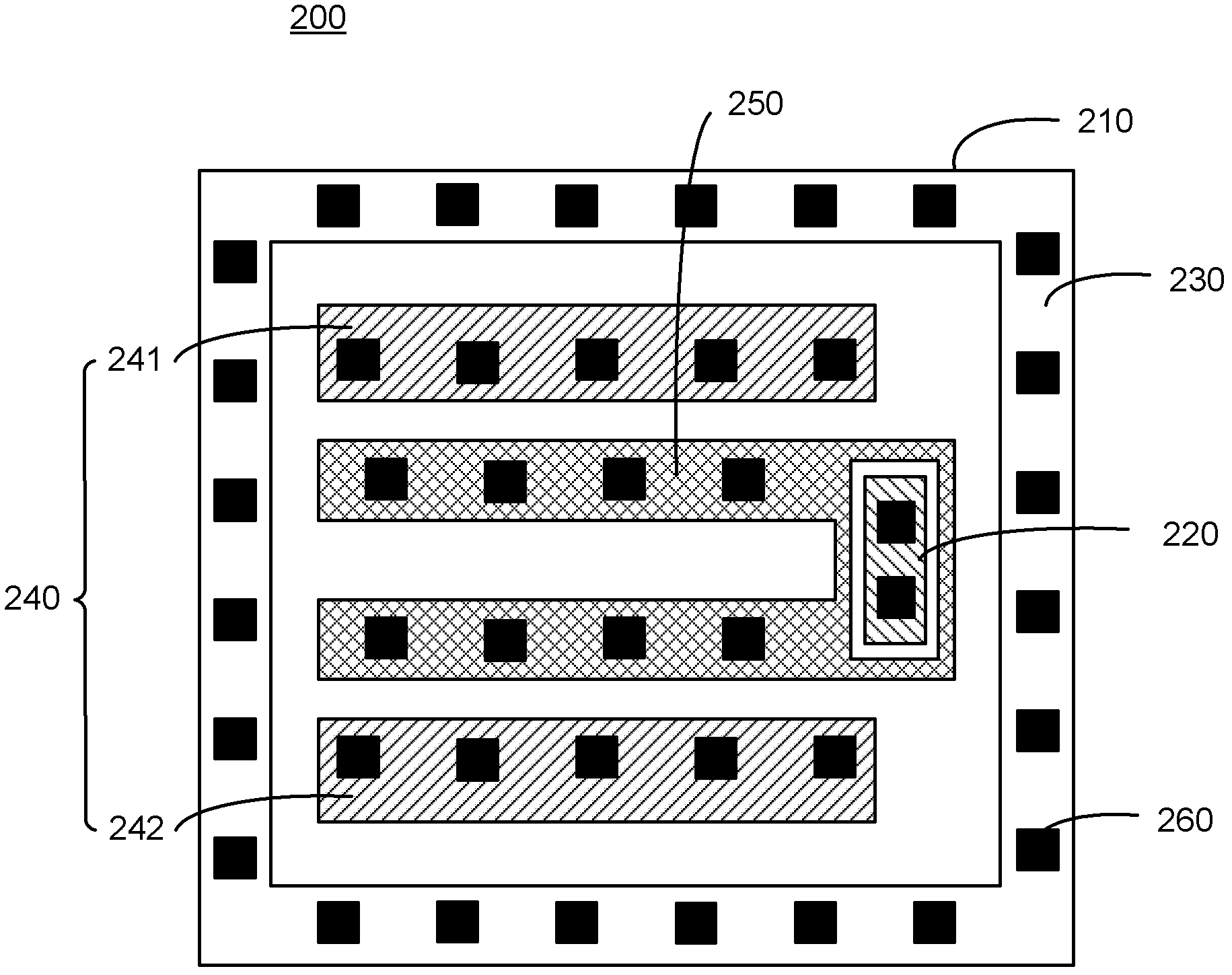

[0035] According to the first embodiment of the present invention, such as figure 2 As shown, the P-type doped region 240 includes a first P-type doped region 241 and a second P-type doped region 242 . The N-type doped region 250 is located between the first P-type doped region 241 and the second P-type doped region 242 . According to the requirements of the process size of the sample to be tested, the width of the N-type doped region 250 can be set, and then the N-type doped region 250 with the width can be tested for doping loss by means of a detection device. If there is a doping loss, the width of the N-type doped region 250 is increased.

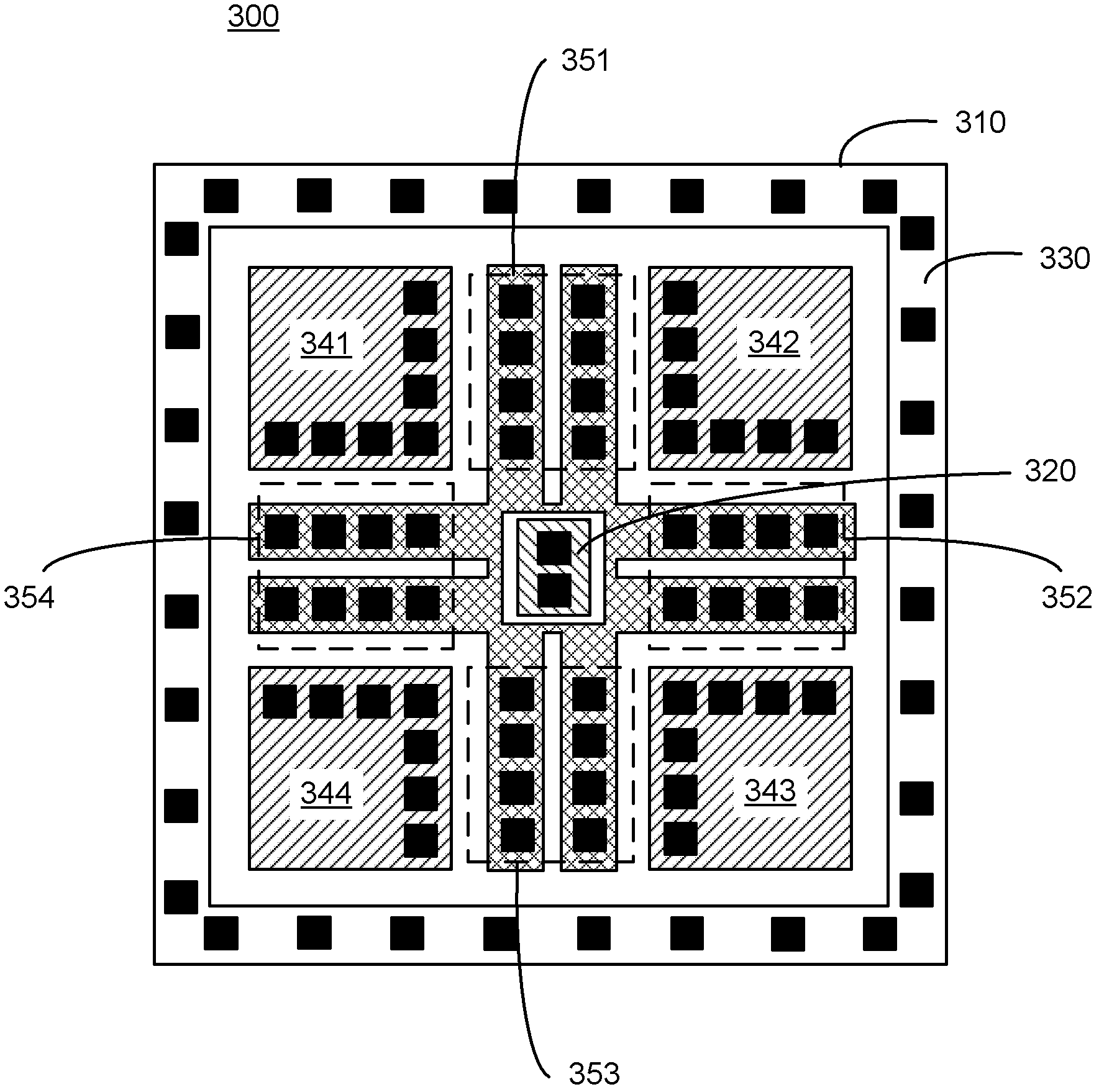

[0036] According to the second embodiment of the present invention, such as image 3 As shown, the P-type doped region includes a first P-type doped region 341 , a second P-type doped region 342 , a third P-type doped region 343 and a fourth P-type doped region 344 . The N-type doped region includes a first N-type doped region 351, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More