Semiconductor failure analysis structure, forming method of semiconductor failure analysis structure and failure time detection method thereof

A failure analysis and failure time technology, which is applied in the direction of single semiconductor device testing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as difficult identification of test equipment, small voltage between test pads, and difficulty in detecting electromigration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment 1

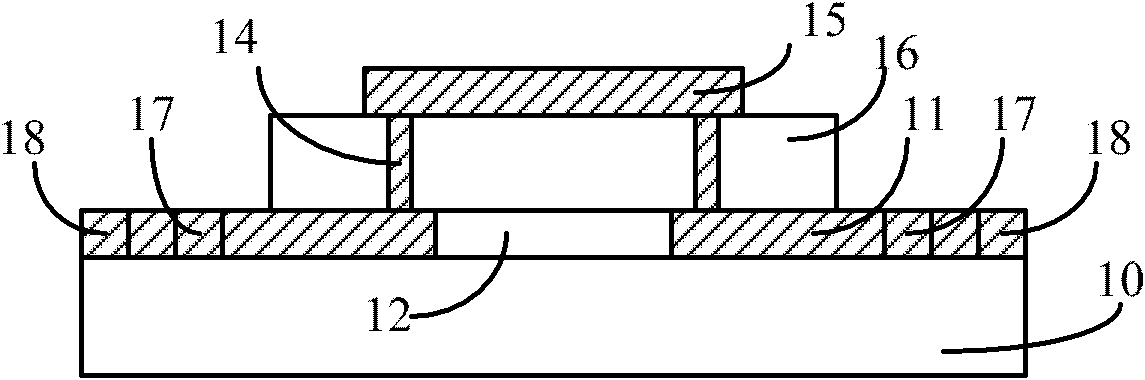

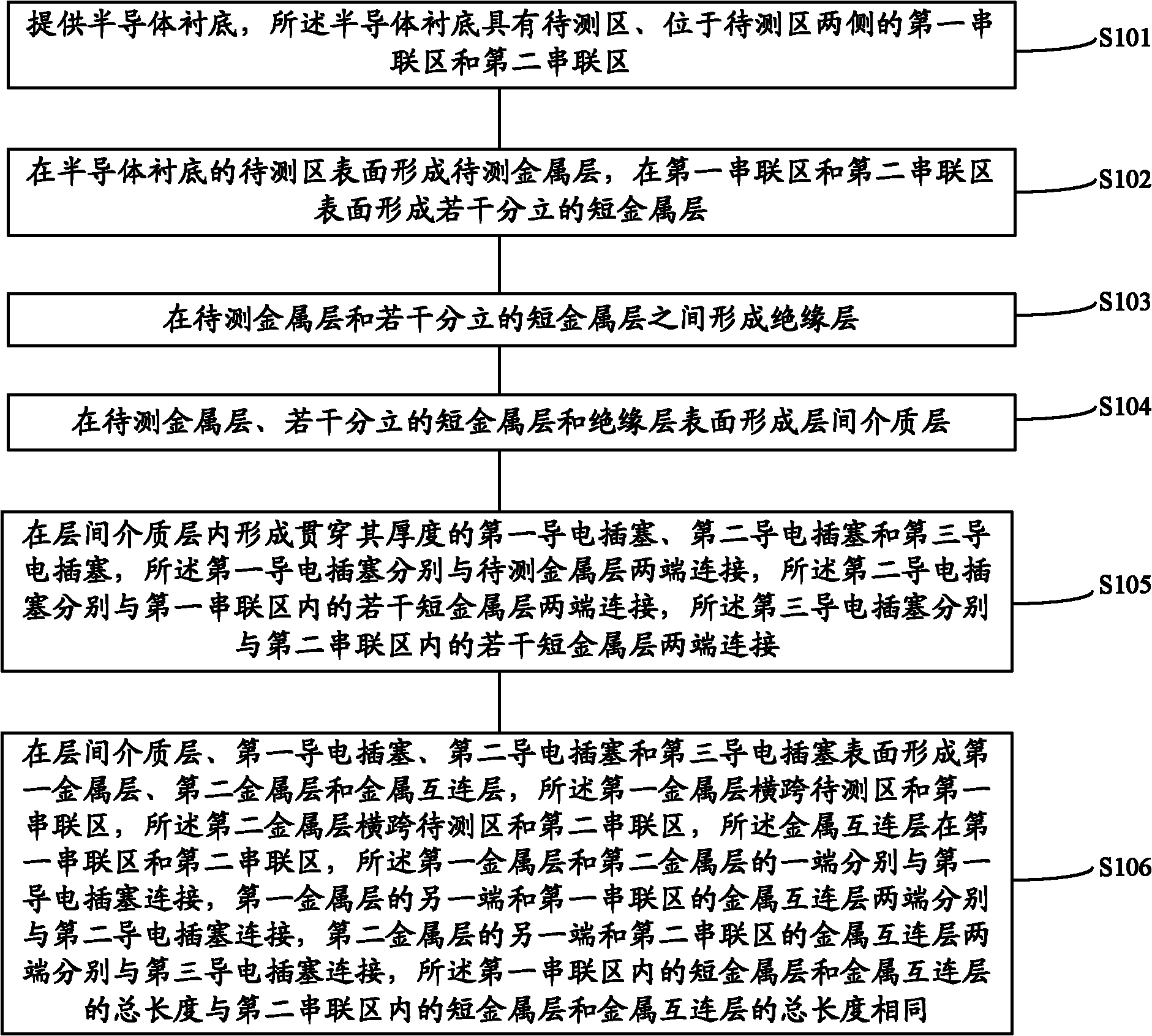

[0094] Please refer to figure 2 , a method for forming a semiconductor failure analysis structure, comprising the following steps:

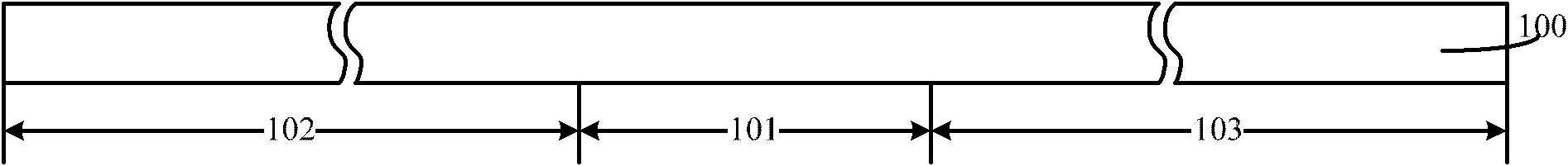

[0095] Step S101, providing a semiconductor substrate, the semiconductor substrate has a region to be tested, a first series region and a second series region located on both sides of the region to be tested;

[0096] Step S102, forming a metal layer to be tested on the surface of the semiconductor substrate to be tested, and forming several discrete short metal layers on the surface of the first serial region and the second serial region;

[0097] Step S103, forming an insulating layer between the metal layer to be tested and several discrete short metal layers;

[0098] Step S104, forming an interlayer dielectric layer on the surface of the metal layer to be tested, several discrete short metal layers, and the insulating layer;

[0099] Step S105, forming a first conductive plug, a second conductive plug, and a third conductive plug through ...

specific Embodiment 2

[0125] Please refer to Figure 7 , a method for forming a semiconductor failure analysis structure, comprising the following steps:

[0126] Step S201, providing a semiconductor substrate, the semiconductor substrate has a region to be tested, a first series region and a second series region located on both sides of the region to be tested;

[0127] Step S202, forming a first metal layer, a second metal layer and a metal interconnection layer on the surface of the semiconductor substrate, the first metal layer straddles the region to be tested and the first series region, and the second metal layer straddles the region to be tested The measurement area and the second series area, the metal interconnection layer is in the first series area and the second series area;

[0128] Step S203, forming an insulating layer between the first metal layer, the second metal layer and the metal interconnection layer;

[0129] Step S204, forming an interlayer dielectric layer on the surface...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Resistance | aaaaa | aaaaa |

| Length | aaaaa | aaaaa |

| Total length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More