LUT (look-up table) structure with MUX (multiplexer) mode and EDA (electronic design automation) optimization method matching with LUT structure

A mode configuration and mode technology, applied to logic circuits using specific components, logic circuits using basic logic circuit components, etc., can solve problems such as poor timing performance and waste of logic resources, to ensure utilization, reduce circuit delay, The effect of saving logic resource overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] In order to make the objectives, technical solutions, and advantages of the present invention clearer, the following further describes the present invention in detail in conjunction with specific embodiments and with reference to the accompanying drawings.

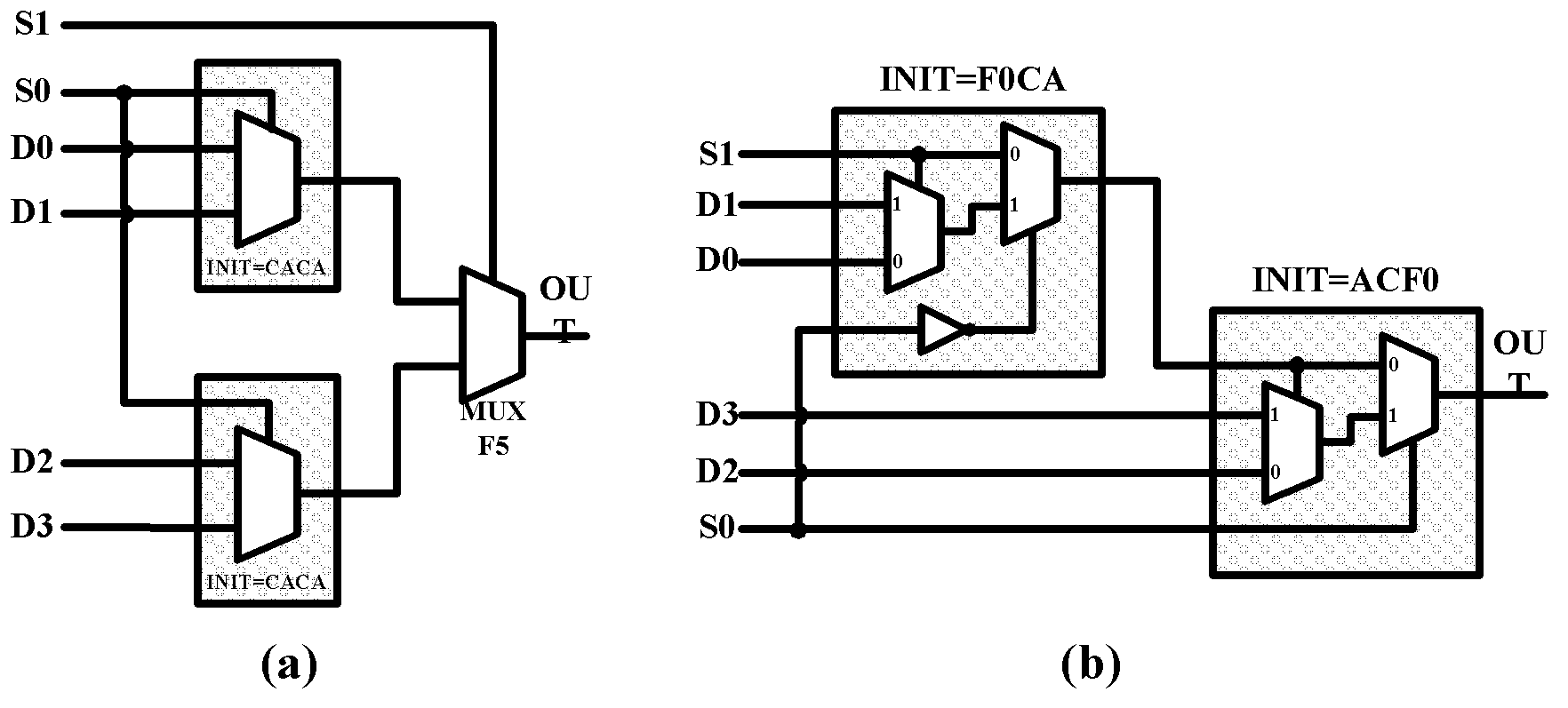

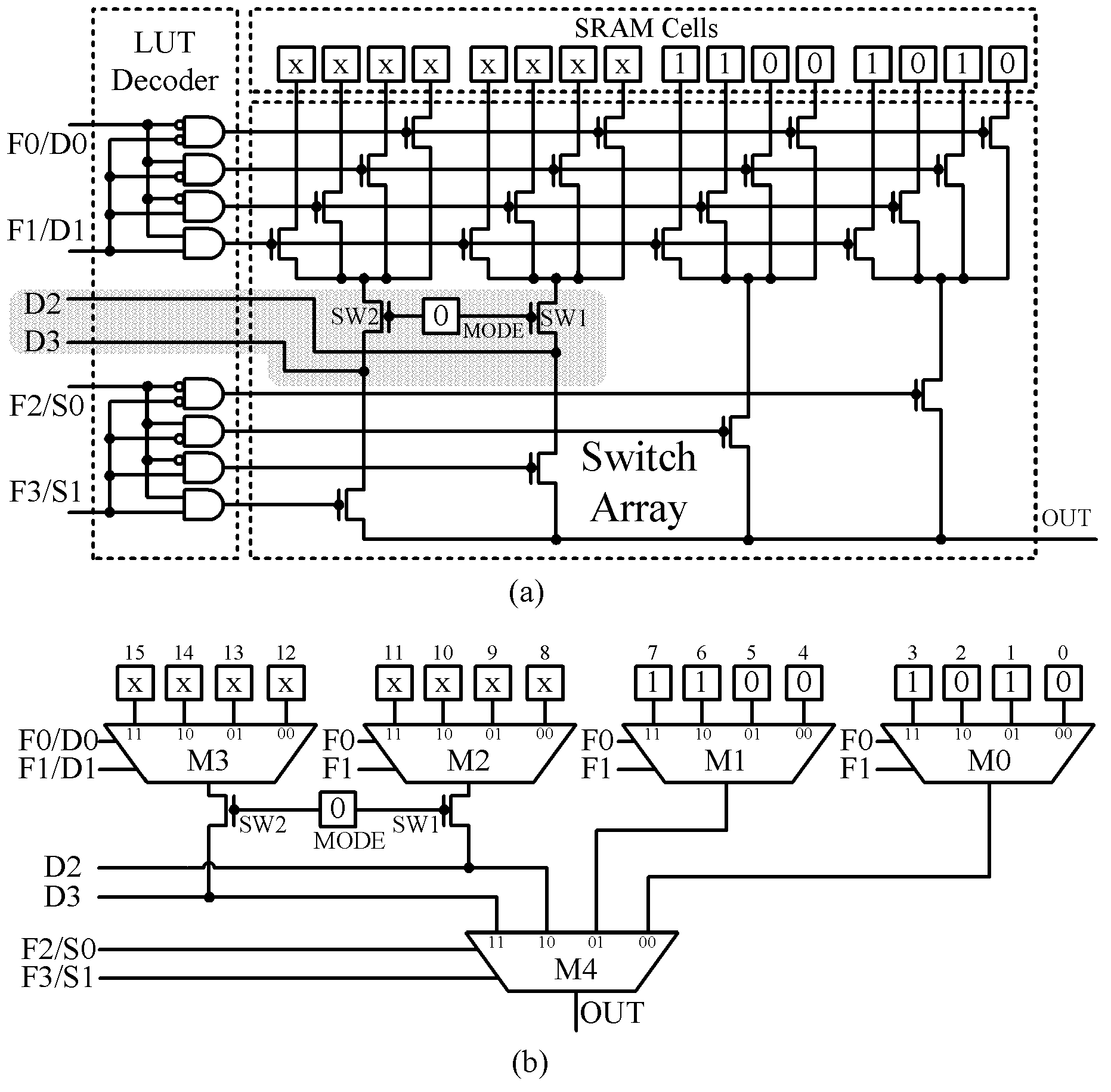

[0039] figure 2 (a) shows the MLUT structure proposed by the present invention, where the part outside the shadow box is a typical traditional LUT structure, and the part inside the shadow box is a structure added on the basis of the traditional LUT. The MLUT structure is based on the traditional LUT structure by adding a mode configuration unit MODE, the first and second N-tube switches (SW1, SW2) directly controlled by the mode configuration unit MODE, and the second and third signal input terminals (D2, D3). Among them, the mode configuration unit MODE is connected between the gates of the first and second N-type switches (SW1, SW2); the drain of the first N-type switch SW1 is connected to the second 4 out of 1 MUX...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com