Method for manufacturing embedded electronic circuit three-dimensional assembly substrate

An electronic circuit and embedded technology, which is applied in the direction of assembling printed circuits, circuits, and electrical solid devices with electrical components, can solve the problems of difficult to guarantee the timing of signal transmission, difficult to achieve technical confidentiality, and difficult to assemble, and to expand the technology. Secrecy way, avoid technology leakage, save space effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

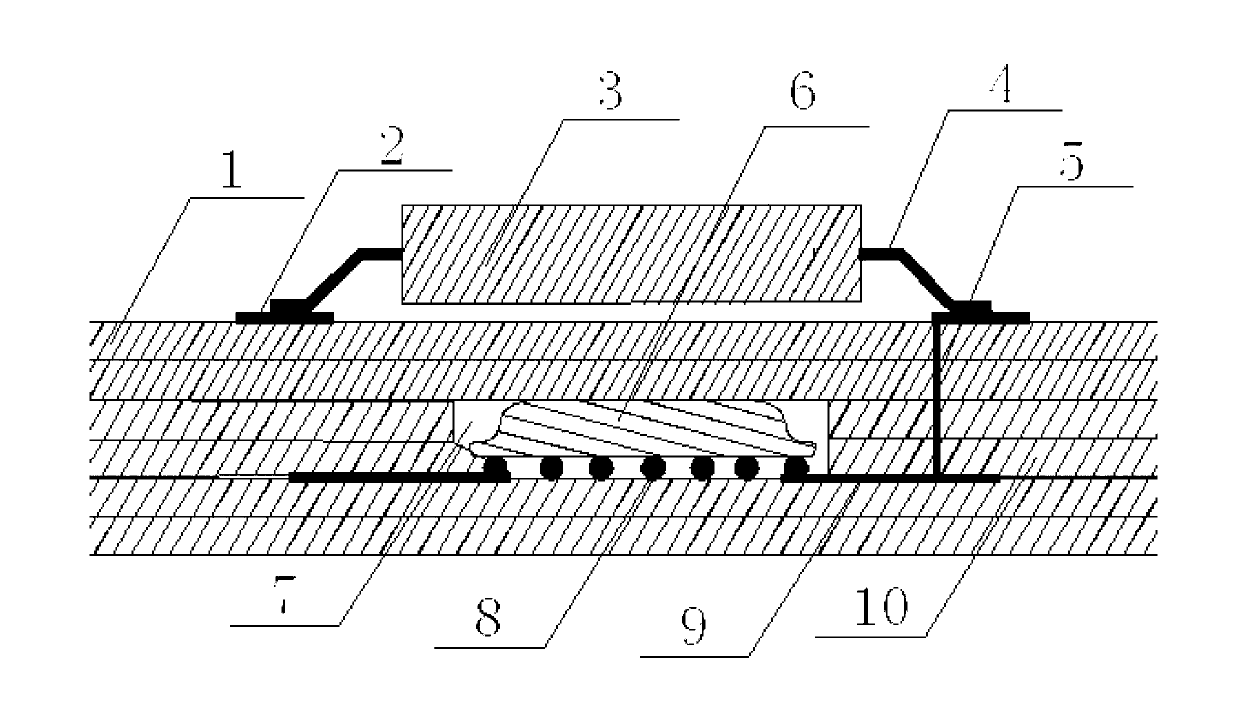

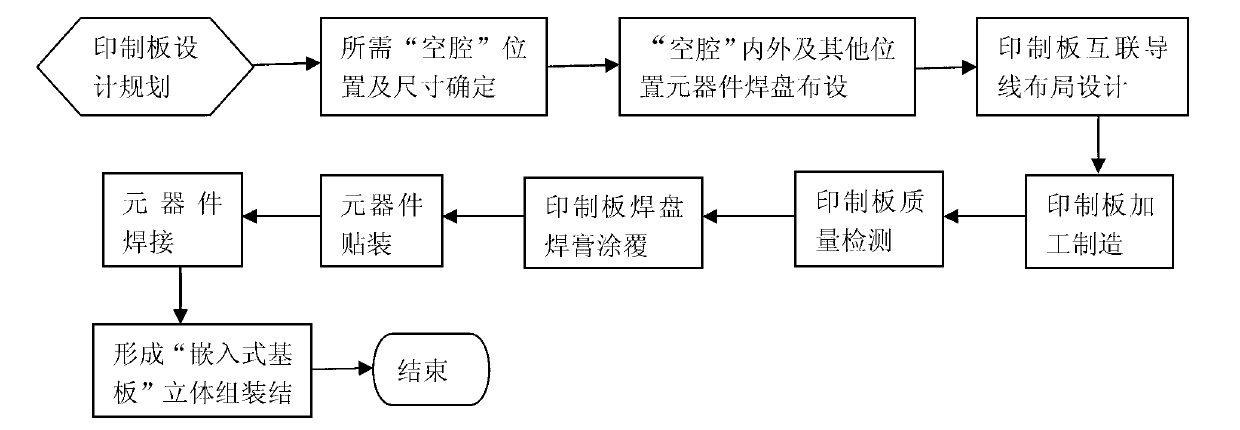

[0022] refer to figure 1 . In the design and manufacturing process of printed circuit components, when designing the layout of printed boards, for some devices, when designing printed boards, according to needs, combined with component packaging, planning and forming printed circuit boards in the printed board substrate 1 Various types of cavities 7 matching the embedded devices in the board, solder joints 8 of embedded components in the printed board, transmission wires 9 in the inner layer of the printed board, and filling materials 10 inside the printed board if necessary. During the manufacturing process of the printed board, the planar printed board is set to be embedded in the embedded substrate, and the cavity 7 whose area and height match the size and height of the layout device and the thickness of the printed board is designed. According to the circuit design, carry out the wiring design and layout of the printed board base material 1, the surface mount device 3, th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More