Circuit board based on SOPC analog brain waves and method for constructing brain dynamic model

A dynamic model and circuit board technology, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve the problems of multiple hardware components, single dot matrix display display, and reduced board dexterity.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

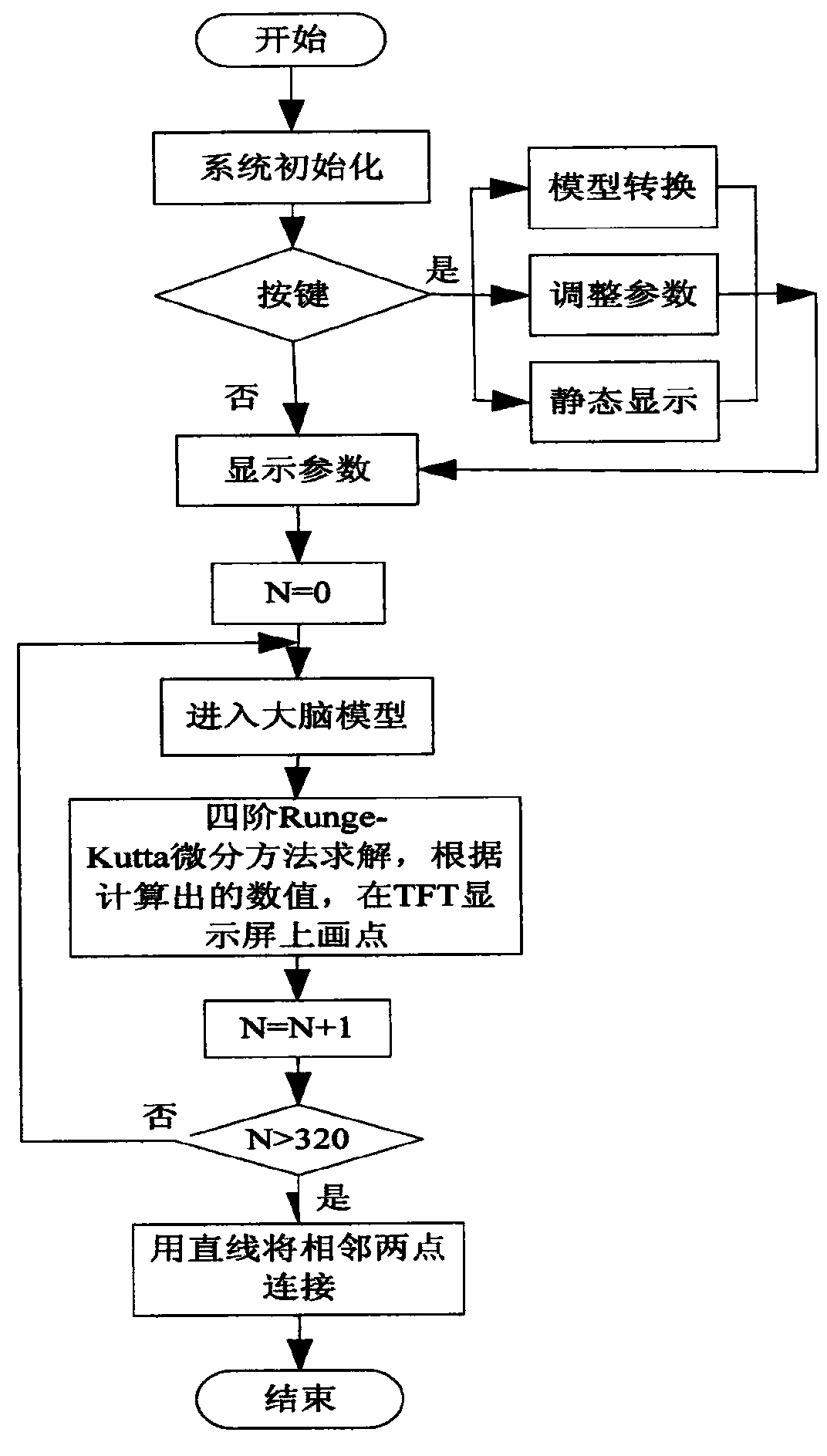

[0022] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

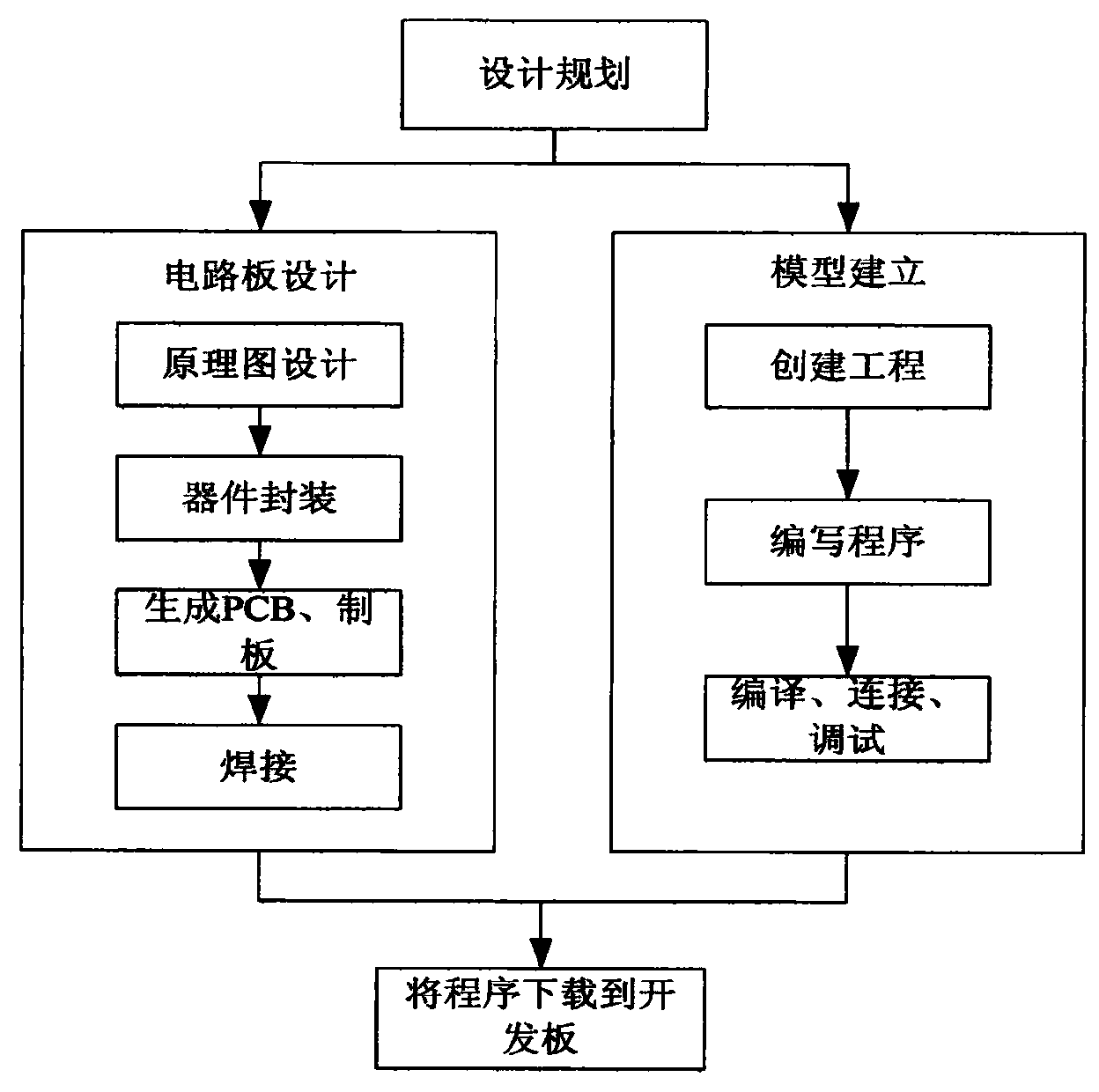

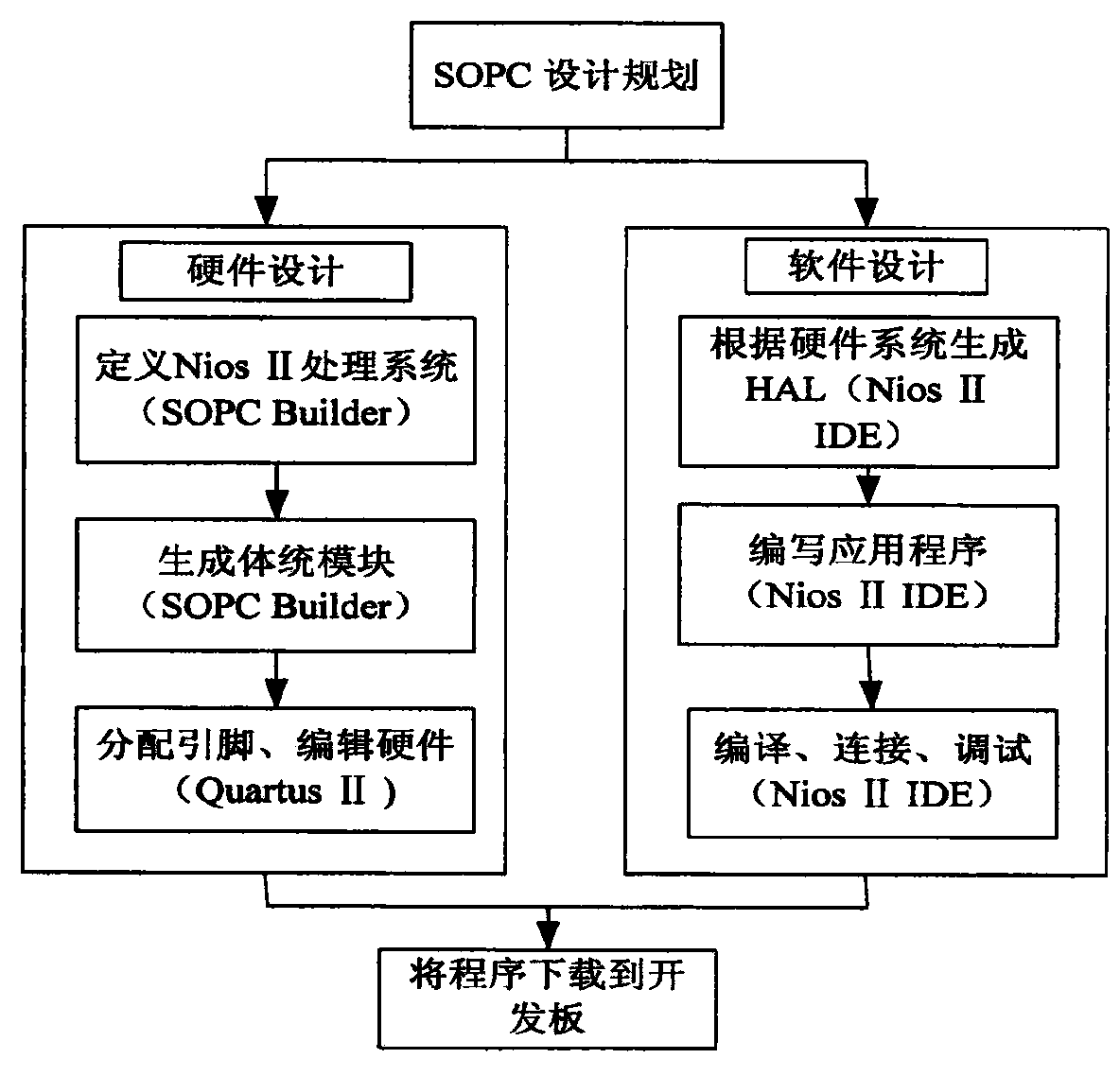

[0023] Such as figure 1 As shown, a circuit board based on SOPC simulating EEG, the circuit board includes: FPGA chip, configuration chip, clock source, SDRAM, FLASH, liquid crystal display, JTAG debugging download interface, buttons.

[0024] The FPGA chip uses the EP2C8Q208C8 chip in the Cyclone II series;

[0025] The configuration chip selects EPCS4. The board provides a 50MHz clock source for the system and uses a phase-locked loop PLL to provide a 50MHz clock for SDRAM with a phase difference of -20deg;

[0026] SDRAM uses K4S511632B-TC75 chip;

[0027] FLASH uses JS28F128J3D-75 chip;

[0028] The display screen adopts a 2.4-inch LCD screen without a touch screen, and the resolution is 240×320;

[0029] The buttons respectively control the conversion of the model, the adjustment of the model parameters, and the static displ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More