Method for manufacturing floating gate MOS transistor

A technology of MOS transistors and manufacturing methods, which is applied in the field of manufacturing floating gate transistors, can solve problems such as cumbersome preparation methods and long production cycles, and achieve the effects of simplifying the process flow, improving production efficiency, and shortening delivery time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The specific embodiment of the present invention will be further described below in conjunction with accompanying drawing:

[0033] The invention provides a method for preparing a floating gate MOS transistor, which can be applied to the technical platform of Flash (memory) and eFlash, and includes the following steps:

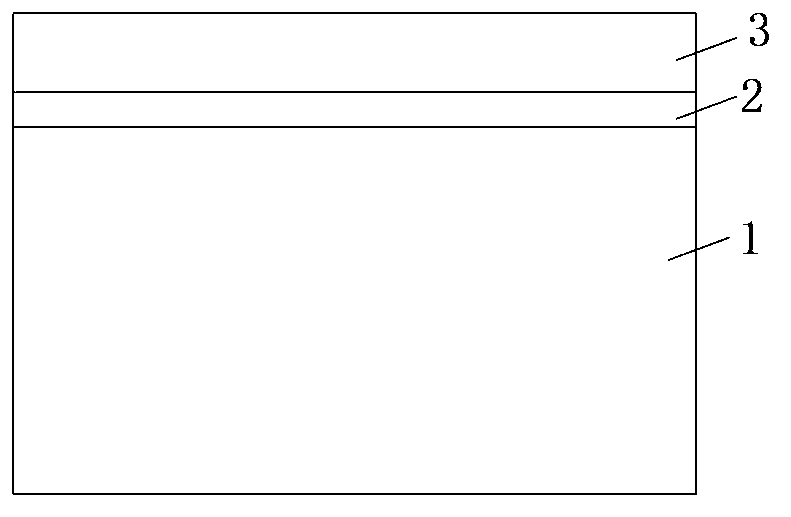

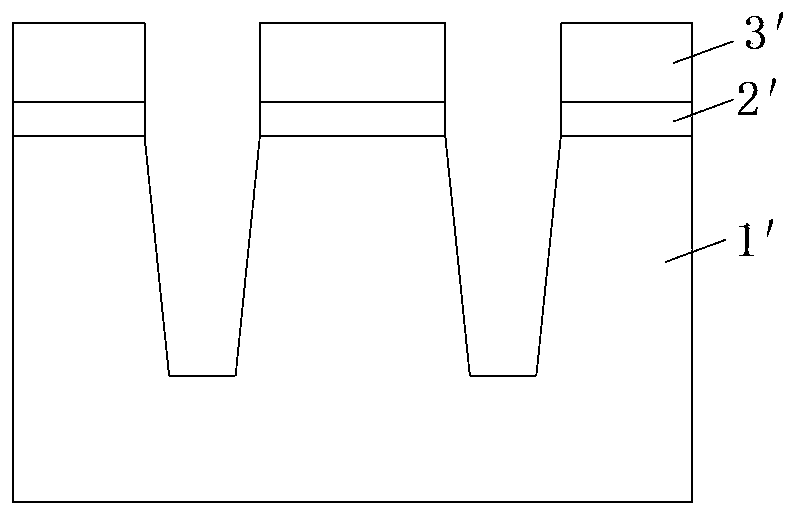

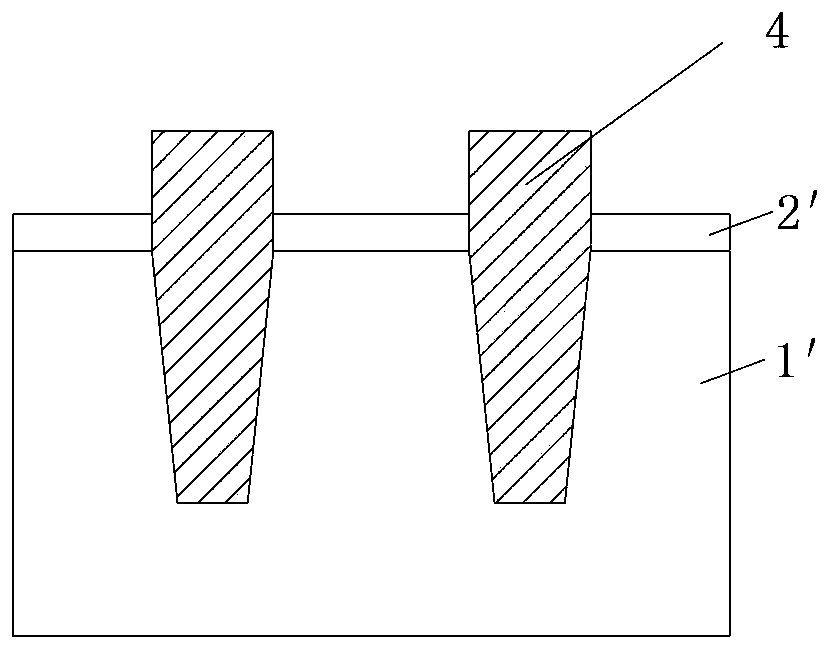

[0034] Step 1. Provide a silicon substrate 1. After depositing a layer of dielectric layer 2 on the upper surface of the silicon substrate, a polysilicon layer 6 and a nitride layer 7 are sequentially deposited on the surface of the dielectric layer 2 from bottom to top. Preferably, the thickness of the deposited polysilicon layer 6 is 600-700 angstroms (such as 600 angstroms, 630 angstroms, 650 angstroms, 680 angstroms, 700 angstroms), and the nitride layer 7 is silicon nitride, such as Figure 6 shown.

[0035] Step 2, coating a layer of photoresist to cover the upper surface of the nitride layer 7, performing an exposure and development process to f...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More