Array substrate, manufacturing method thereof and display device

A technology for array substrates and manufacturing methods, applied in the fields of array substrates and their manufacturing methods, and display devices, can solve problems such as poor channels, affecting product quality, and failure to improve mask output, so as to reduce manufacturing processes, improve product quality, and Avoid the effect of TFT channel bad

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

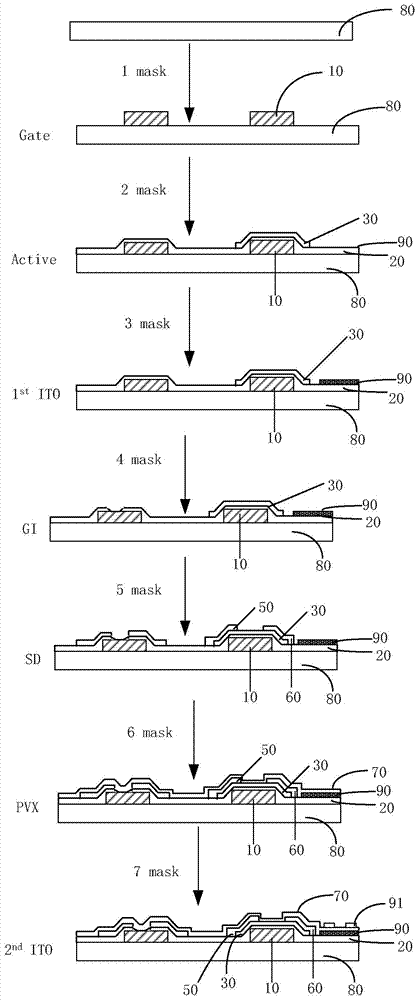

[0088] The principles and features of the present invention are described below in conjunction with the accompanying drawings, and the examples given are only used to explain the present invention, and are not intended to limit the scope of the present invention.

[0089] It should be noted that the "upper" in "X is arranged on Y" mentioned in the present invention includes the meaning that X is in contact with Y and that X is located above Y. In the present invention, as shown in the accompanying drawings, the The base substrate is defined as being arranged at the bottom; the patterning process referred to in the present invention includes processes such as photoresist coating, masking, exposure, development, etching, and photoresist stripping. as an example.

[0090] Preferred embodiments of the TFT-LCD array substrate provided by the present invention are described below.

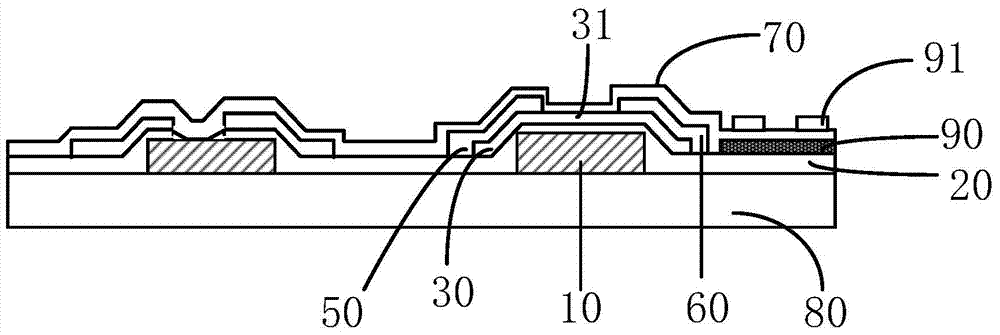

[0091] The TFT-LCD array substrate of this embodiment mainly includes gate lines, data lines, TFTs a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com