Method for manufacturing fin field effect tube

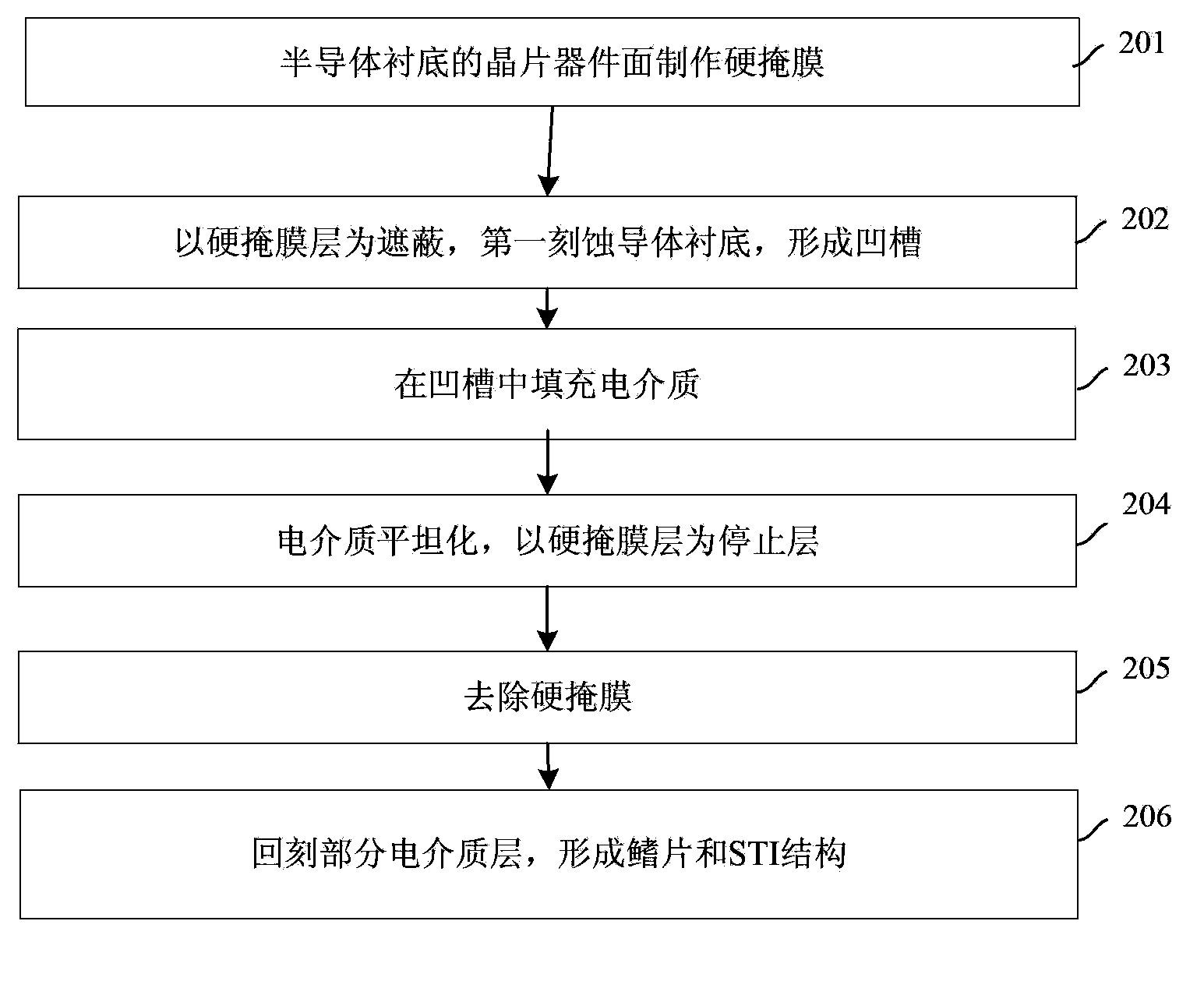

A technology of a fin field effect transistor and a manufacturing method, which is applied in the manufacture of semiconductor/solid state devices, electrical components, semiconductor devices, etc., can solve the problem that the Fin step engraving process is not easy to control, affects the height and shape of fins, and has a high aspect ratio concave Difficulties in trench etching and filling processes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment 1

[0055] combine Figure 10~16 Illustrate the present invention as Figure 9 The specific steps for the fabrication of the FinFET shown are as follows:

[0056] Step 901, Figure 10 Schematic diagram of the cross-sectional structure of the FinFET manufacturing step 901 of the present invention, such as Figure 10 As shown, a silicon germanium (SiGe) layer 101 and a silicon (Si) layer 102 are epitaxially grown on the wafer device surface of the semiconductor substrate 100 in sequence;

[0057] In this step, a wafer with a semiconductor substrate 100 is provided, and the semiconductor substrate 100 is bulk silicon or silicon-on-insulator SOI; the thickness of the epitaxially grown SiGe layer 101 ranges from 5 nanometers (nm) to 50 nanometers, for example: 5 nanometers , 20 nanometers or 50 nanometers; the thickness range of the epitaxial growth Si layer 102 is 10 nanometers to 100 nanometers, for example: 10 nanometers, 50 nanometers or 100 nanometers; the thickness of the SiGe...

specific Embodiment 2

[0075] combine Figure 18~24 In the present invention, such as Figure 17 The specific steps of the FinFET fabrication shown are as follows:

[0076] Step 1001, Figure 18 Schematic diagram of the cross-sectional structure of the FinFET manufacturing step 1001 of the present invention, such as Figure 18 As shown, a silicon germanium (SiGe) layer 101 and a silicon (Si) layer 102 are epitaxially grown on the wafer device surface of the semiconductor substrate 100 in sequence;

[0077] In this step, a wafer with a semiconductor substrate 100 is provided, and the semiconductor substrate 100 is bulk silicon or silicon-on-insulator SOI; the thickness of the epitaxially grown SiGe layer 101 ranges from 5 nanometers (nm) to 50 nanometers, for example: 5 nanometers , 20 nanometers or 50 nanometers; the thickness range of the epitaxial growth Si layer 102 is 10 nanometers (nm) to 100 nanometers, for example: 10 nanometers, 50 nanometers or 100 nanometers; the SiGe layer 101 and the ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More