A dummy synthesis optimization method based on cmp simulation model

An optimization method and simulation model technology, which is applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problems that the filling constraints are too conservative, and the final dummy effect cannot be guaranteed.

- Summary

- Abstract

- Description

- Claims

- Application Information

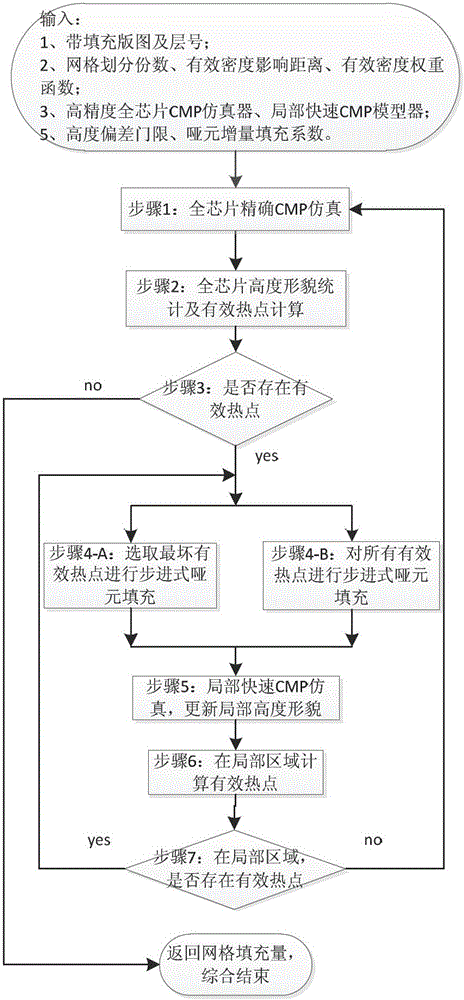

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

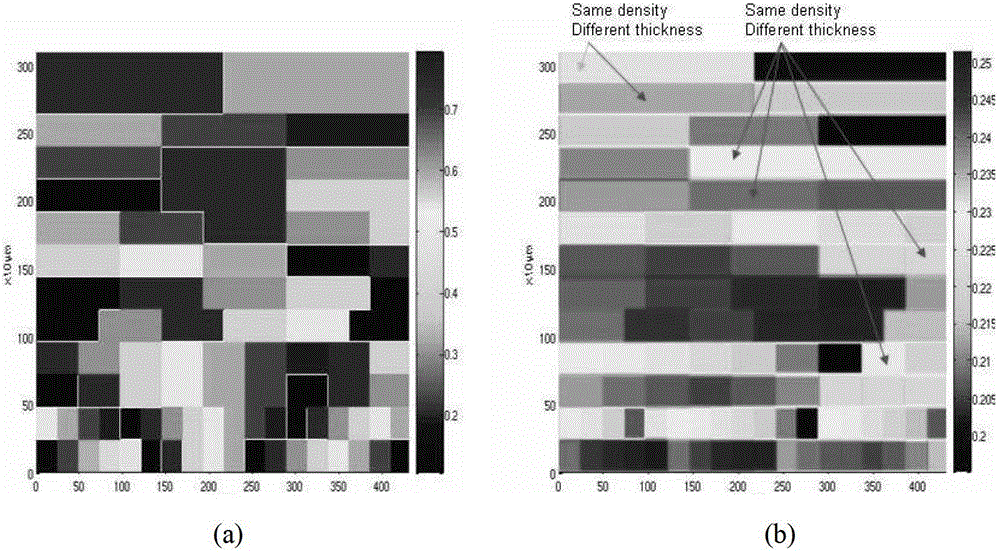

[0106] Embodiment 1 Comparison between the method of the present invention and the traditional rule-based dummy synthesis method on the CMP height topography results

[0107] The purpose of introducing CMP model simulation in the dummy filling process is to obtain a smoother chip surface after CMP polishing the filled layout. We use a full-chip CMP simulator to simulate the layout obtained by different dummy filling methods, calculate the mean square error of the chip surface height profile, and use this value to measure the filling quality of different dummy filling methods. The smaller the mean square error, the better the flatness of the chip surface, and the better the effect of dummy filling. The formula for calculating the mean square error is:

[0108]

[0109] Among them, h mean Same definition as formula (1).

[0110] In order to compare the filling effects of different dummy filling methods under the same filling amount, we changed the height deviation threshol...

Embodiment 2

[0111] Embodiment 2 The comparison between the method of the present invention and the traditional rule-based dummy synthesis method on CPU computing time

[0112] In this embodiment, different dummy filling methods are tested on problems of different scales. Figure 7 Execution times for 3 different filling methods are given. It can be seen from the figure that the linear programming method is the fastest to solve small-scale problems, but because its time complexity is O(n 3 ), the time increases rapidly. The two dummy filling methods based on the CMP model simulation need to call the CMP simulator repeatedly, and the time overhead is large, but the important thing is that they are not sensitive to the problem scale. The experimental data shows that the time complexity is about O(n), so In large-scale problems, it is much faster than the density-driven linear programming method.

[0113] Comparing the two model-based dummy filling methods, the FMF method is about 6 times ...

Embodiment 3

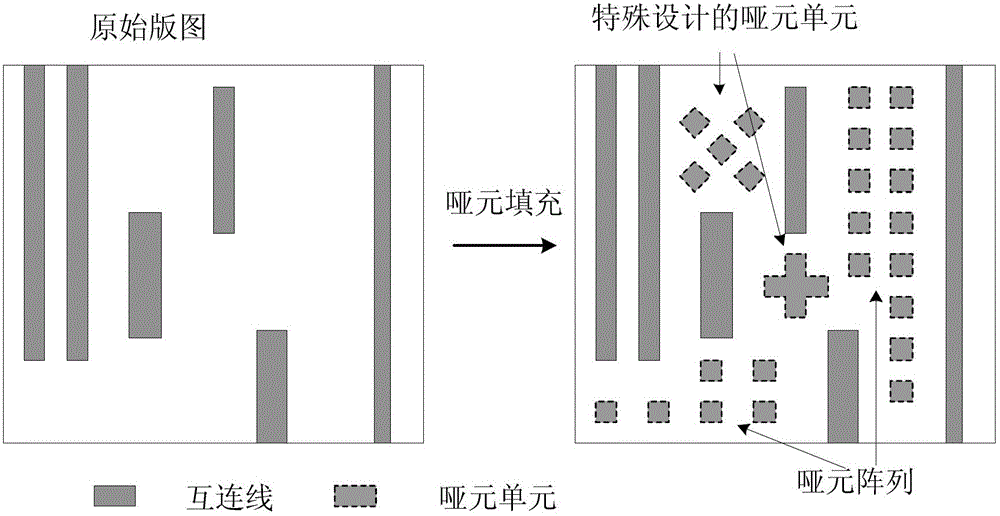

[0114] Embodiment 3 Comparison between the method of the present invention and the traditional rule-based dummy element synthesis method after filling the layout graphic features

[0115] In order to further analyze the difference in filling effect between the dummy filling method based on CMP model simulation and the dummy filling method driven by density rules, Table 1 counts the graphic features of the layout obtained by different dummy filling methods. In Table 1, three The number of dummy insertions of the two methods is basically the same.

[0116] Table 1 The density distribution characteristics of the results of different dummy filling methods

[0117]

[0118] As can be seen from Table 1, the minimum window density after filling (0.26) of the density rule-driven method is much higher than that of the two model-based dummy filling methods (0.187 and 0.193, respectively). In fact, this value is the lower bound of the window density. The density rule-driven method f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More