Tunneling field effect floating gate transistor and manufacturing method thereof

A floating gate transistor and tunneling field effect technology, which is applied in the field of device manufacturing, can solve problems such as data loss and hinder the escape of floating gate electrons, and achieve the effects of improved data storage time, wide application, and low production cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The following description is a preferred embodiment embodying the principles of the present invention. It should be noted that the accompanying drawings are schematic diagrams of idealized embodiments of the present invention, and the shapes and sizes shown in each part do not represent actual shapes and sizes. But it still fully reflects the mutual position between the area and each part, especially the up-down and adjacent relationship between components.

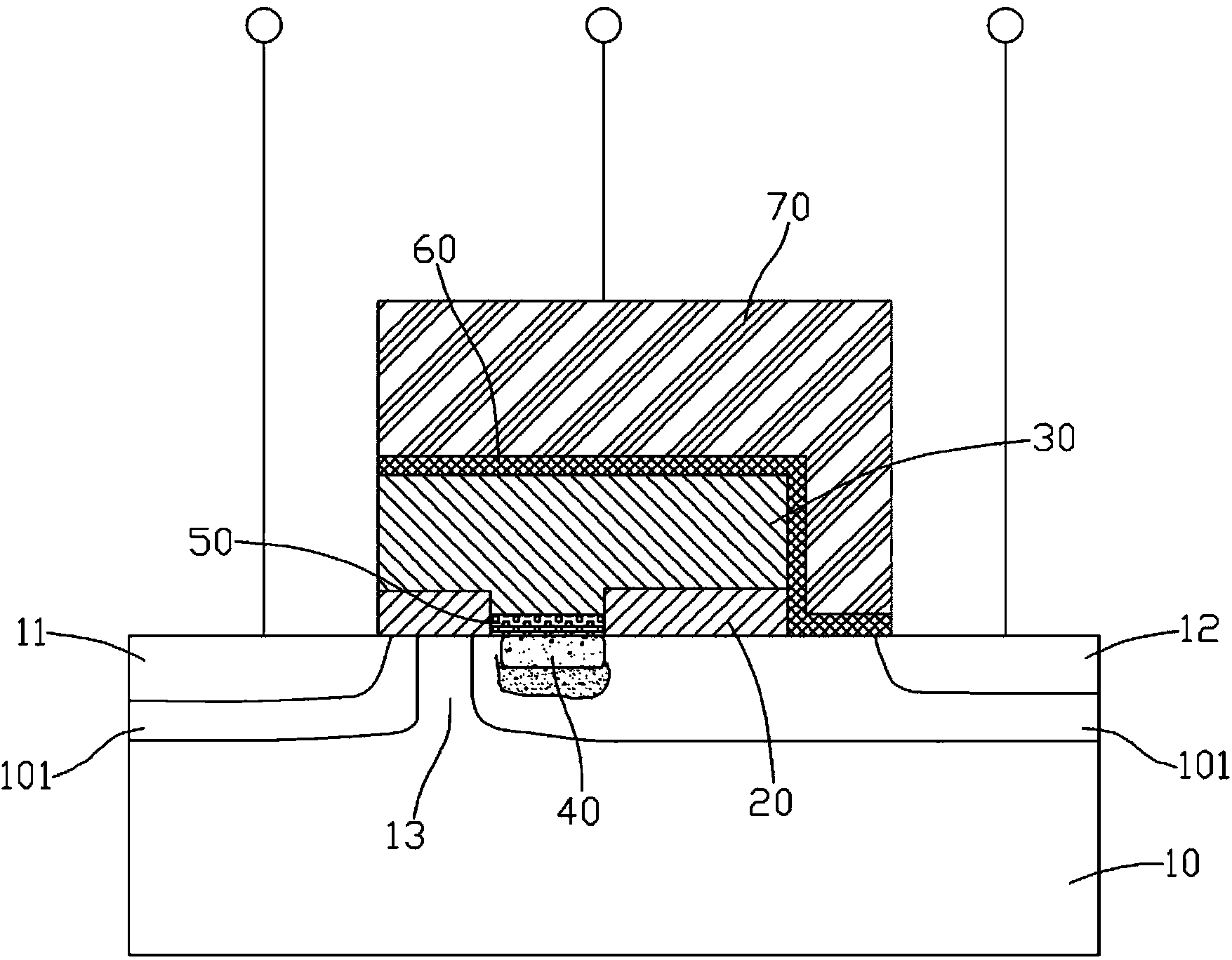

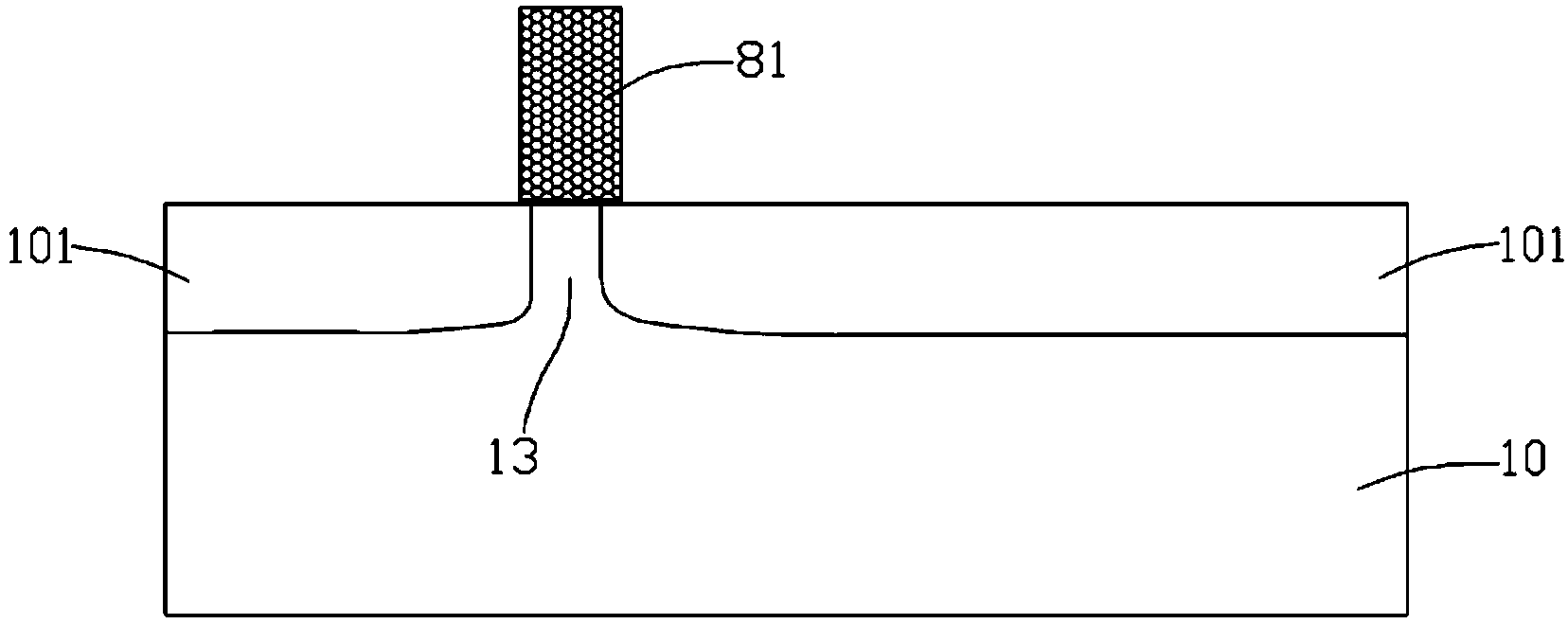

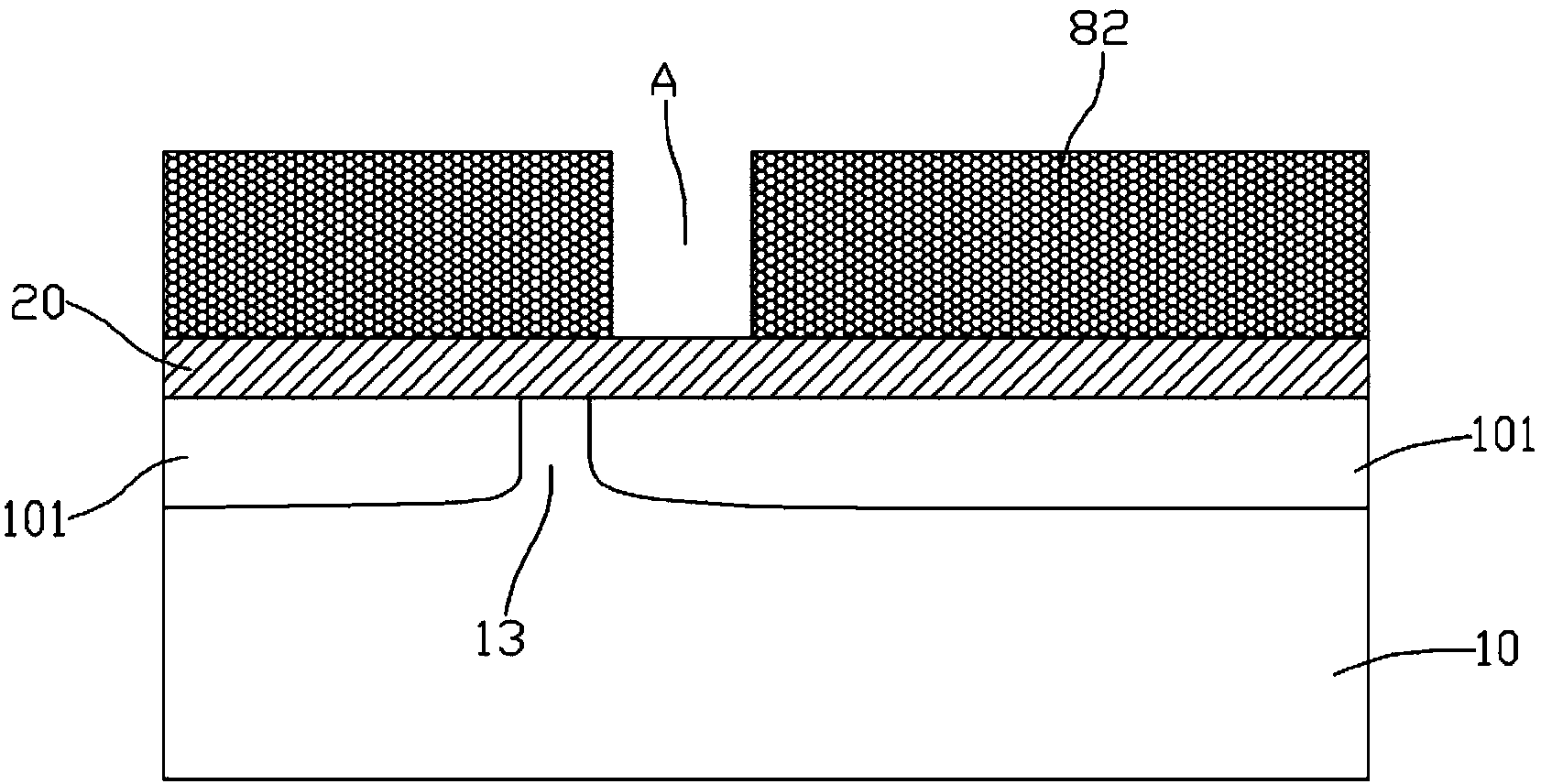

[0042] See figure 1 As shown in the cross-sectional view along the channel direction, the tunneling field effect floating gate transistor of the present invention includes the following parts:

[0043] a semiconductor substrate 10 with a first doping type;

[0044] A source 11 and a drain 12 having a second doping type formed on the semiconductor substrate 10;

[0045] a channel region 13 formed in the semiconductor substrate 10 between the source electrode 11 and the drain electrode 12;

[0046] A first insulat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com