Method for directly extracting small-signal model parameters of III-V MOSFET

A small signal model, III-V technology, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as deviation and deviation from physical meaning

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0065] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

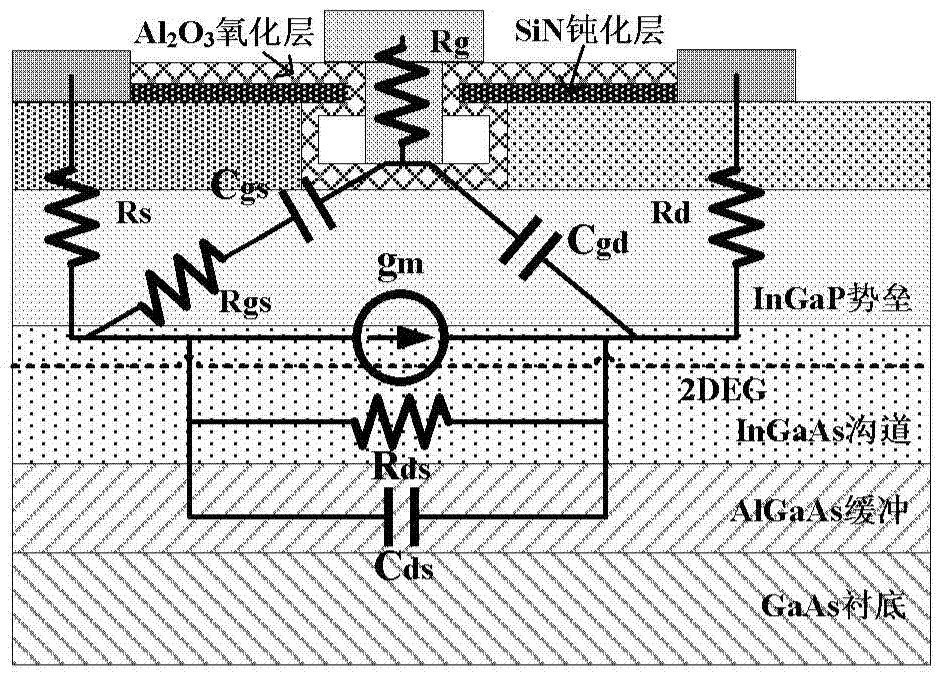

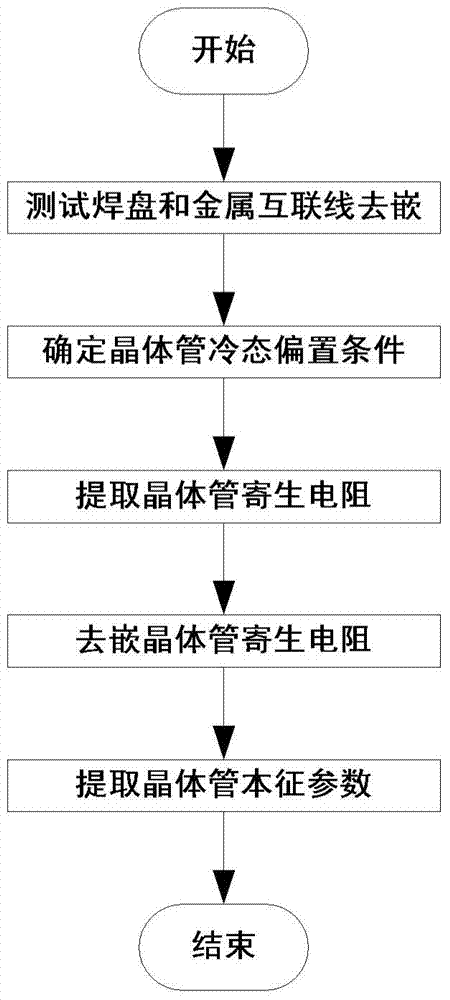

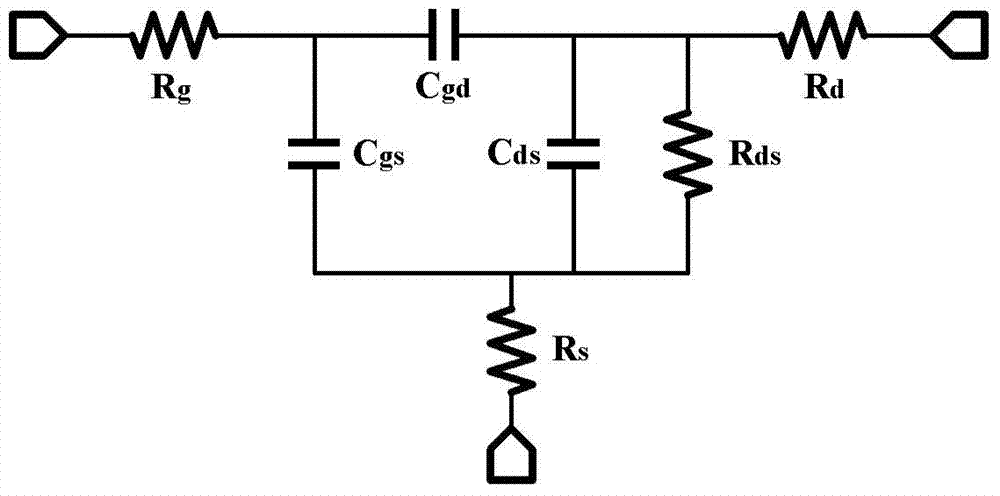

[0066] The method for directly extracting small-signal model parameters of this III-V family MOSFET provided by the present invention is to de-embed through pads and metal interconnection lines, and use transistor DC transfer characteristics and cold-state S parameters to determine the appropriate bias when extracting transistor parasitic resistance. Under this bias condition, the influence of the channel resistance is removed, the parasitic resistance parameters are extracted by linear fitting, and finally the parasitic resistance is de-embedded, and the small-signal model equivalent circuit and curve fitting of the III-V MOSFET are used to extract the characteristic parameters, the method specifically includes the follow...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More