A Dual Mode Electrostatic Discharge Protection I/O Circuit

A technology for electrostatic discharge protection and circuit protection. It is used in static electricity, circuits, electrical components, etc., and can solve problems such as electrostatic discharge damage, device breakdown, and breakdown failure.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

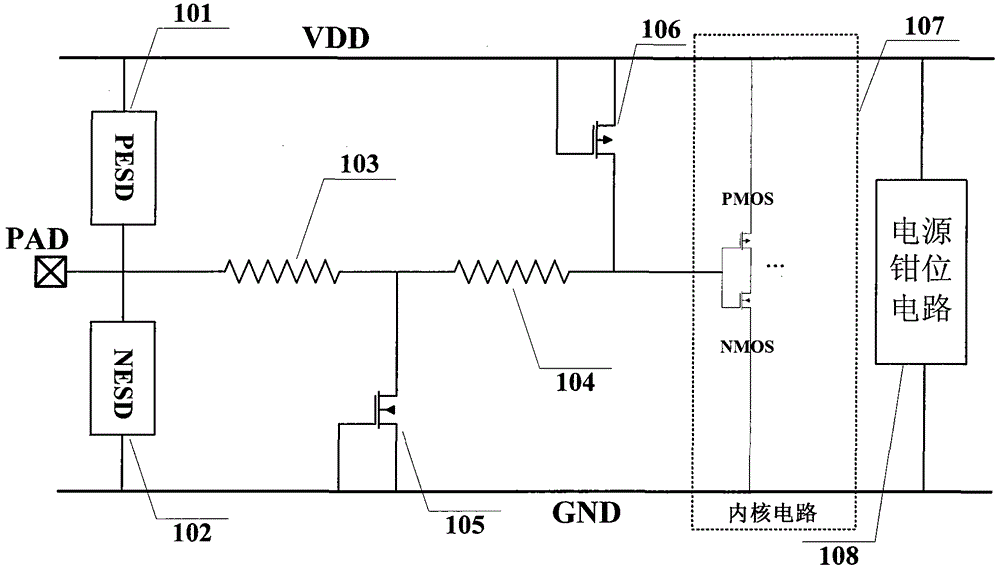

[0014] The present invention is a dual-mode electrostatic discharge protection I / O circuit, which can not only realize the protection of HBM discharge, but also provide protection for E-Gun model discharge. The implementation plan is as follows:

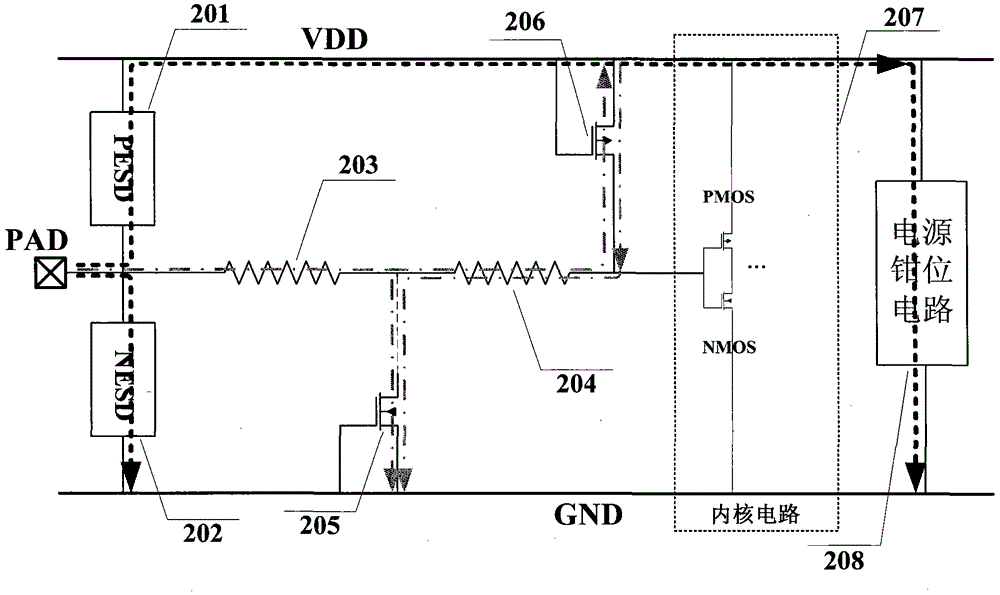

[0015] Such as figure 2 , is the discharge path when the I / O circuit E-Gun model of the present invention discharges. Take the I / O-GND forward 2000V electrostatic discharge as an example, at this time, GND is grounded, and the positive charge electrostatic discharge is performed on the I / O PAD.

[0016] First, the NESD 202 of the primary protection will be turned on and discharged, forming a figure 2 The high-current discharge path from PAD to GND through 202 is one of the main electrostatic discharge paths. At this time, the voltage at the PAD terminal will exceed 10V, so the secondary protection NMOS205 will also be turned on, clamping the core circuit to GND at a safe level, and at the same time, due to the function of the inp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More