Method of causing partially-configurable FPGA (Field Programmable Gate Array) chip system to have high reliability

A chip system and reliability technology, applied in the direction of program control device, program loading/starting, etc., can solve the problems of complex design and difficult implementation, and achieve the effects of improving reliability, overcoming large resource consumption, and overcoming complex design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

[0034] The present invention proposes a highly reliable implementation method based on a partially configurable FPGA chip system, which performs repeated partial configuration on the FPGA chip without affecting the normal operation of the chip, to eliminate accumulated logic errors, and has the characteristics of low resource consumption .

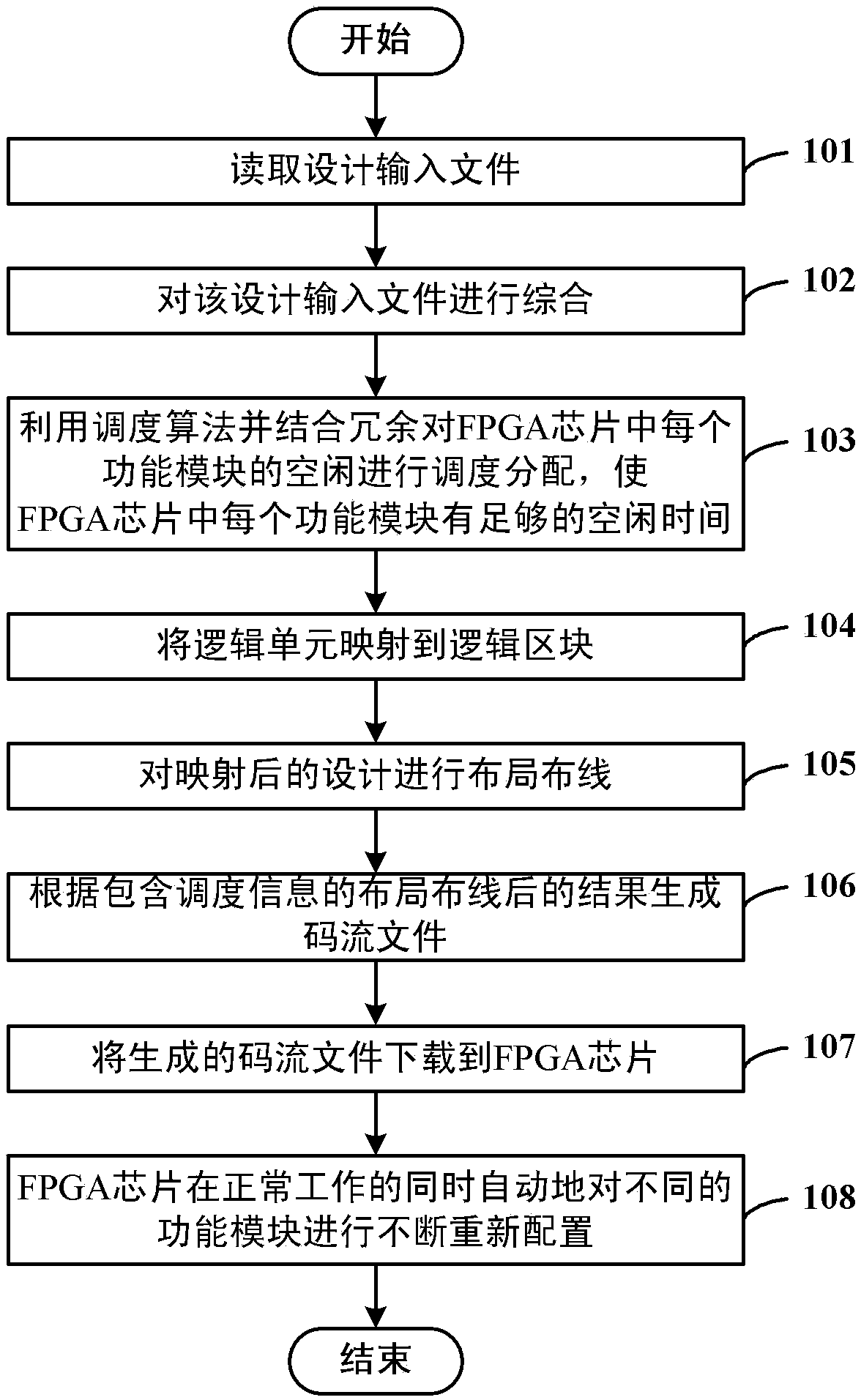

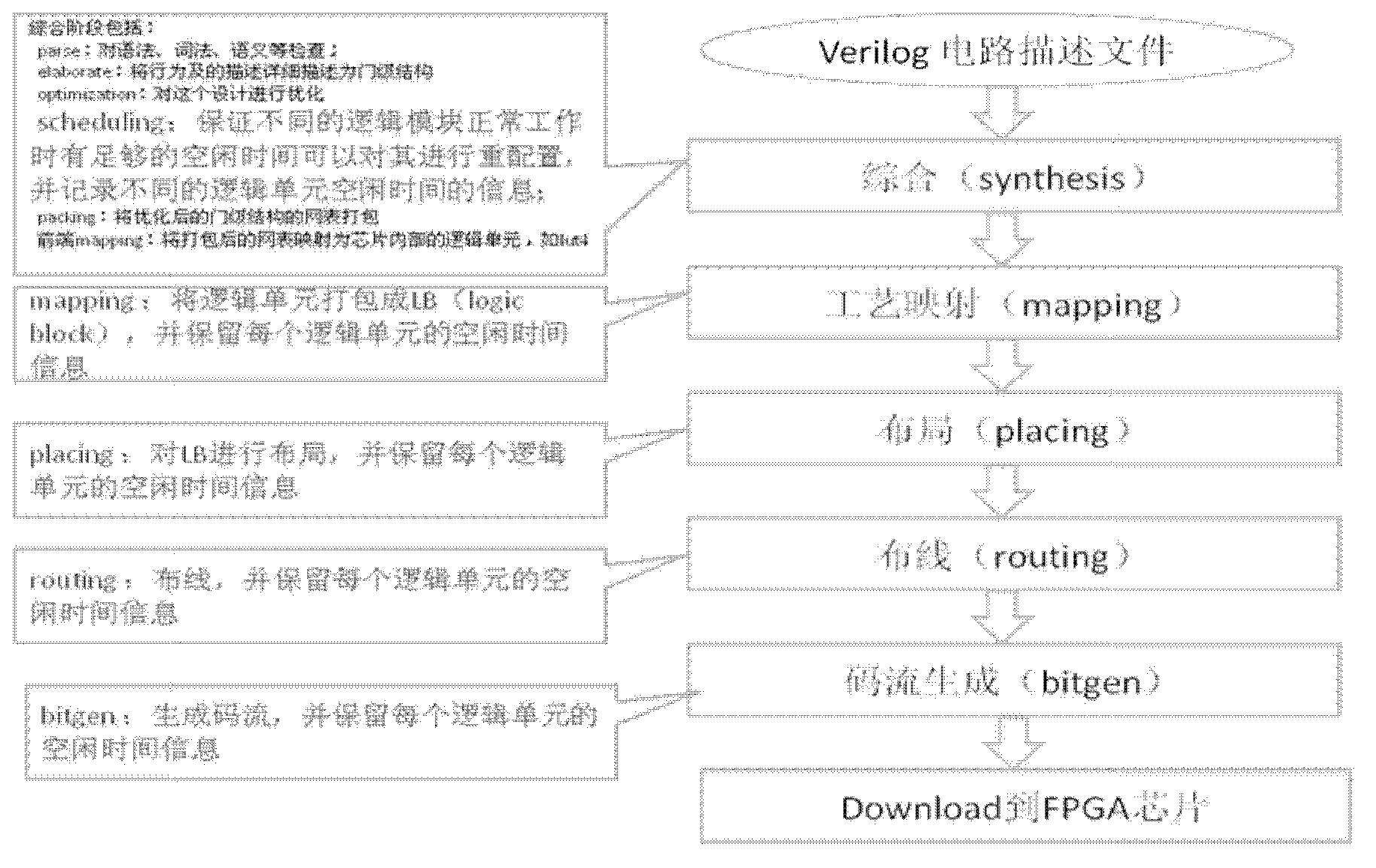

[0035] like figure 1 as shown, figure 1 It is a flow chart of a method for making a partially configurable FPGA chip system with high reliability provided by the present invention. The FPGA chip supports partial configuration, and the method includes the following steps:

[0036] Step 101: read the design input file; the design input file includes a design file described by Verilog ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More