FPGA (field programmable gate array)-based permanent magnet synchronous motor current loop bandwidth expansion device

A permanent magnet synchronous motor and bandwidth expansion technology, which is applied in the control of electromechanical transmission, control of generators, motor generator control, etc., can solve low-delay bandwidth, low bandwidth, and delay of permanent magnet synchronous motor current control loop To achieve the effect of improving the bandwidth of the current loop, improving the overall performance, and optimizing the timing of the current control

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

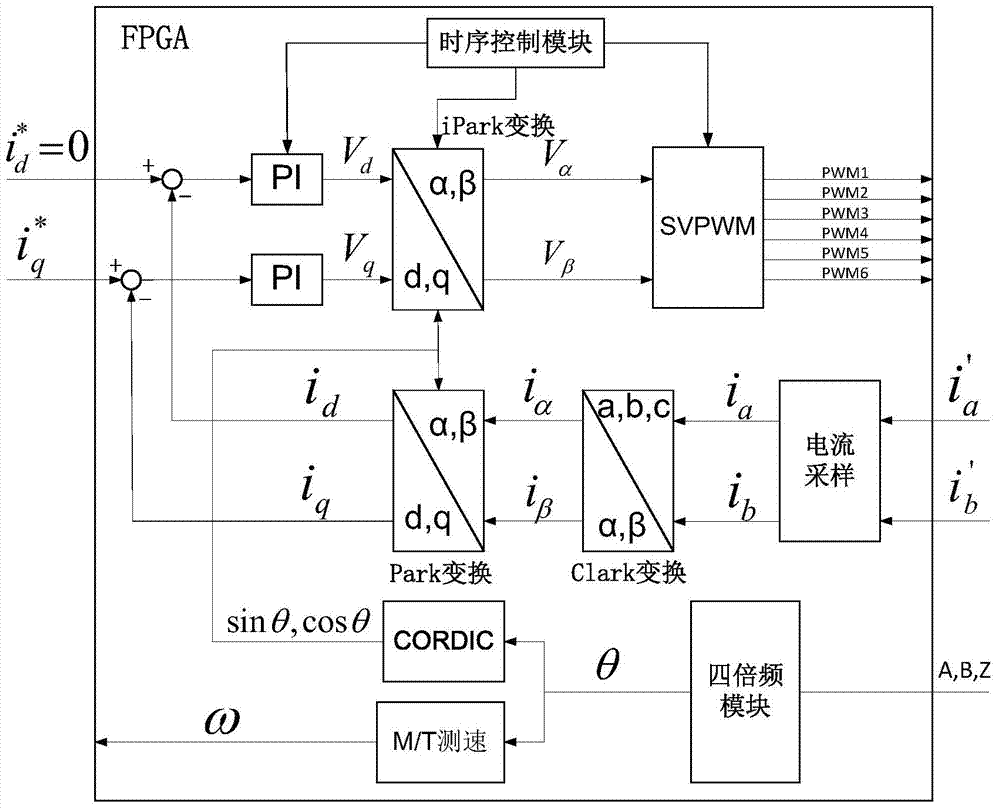

[0033] In order to make the object, technical solution and advantages of the present invention more clear, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention. In addition, the technical features involved in the various embodiments of the present invention described below can be combined with each other as long as they do not constitute a conflict with each other.

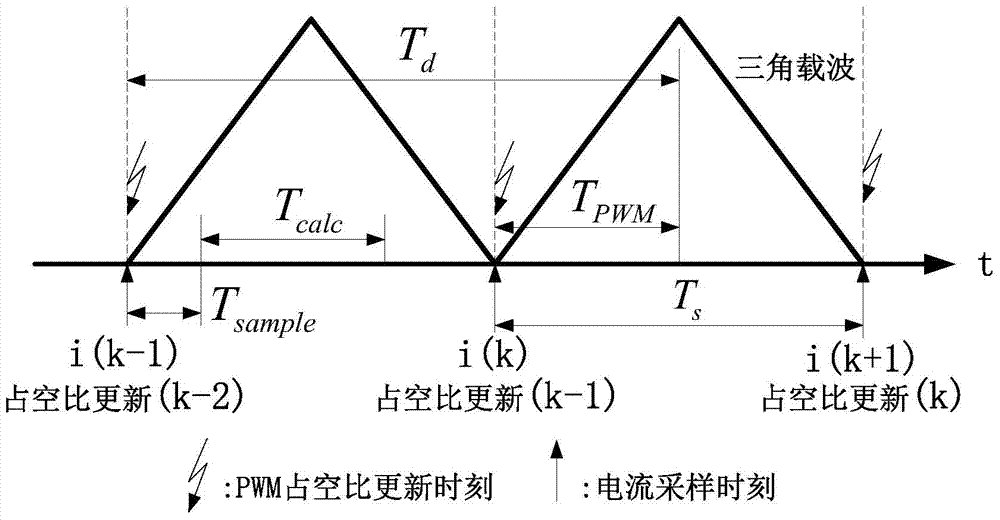

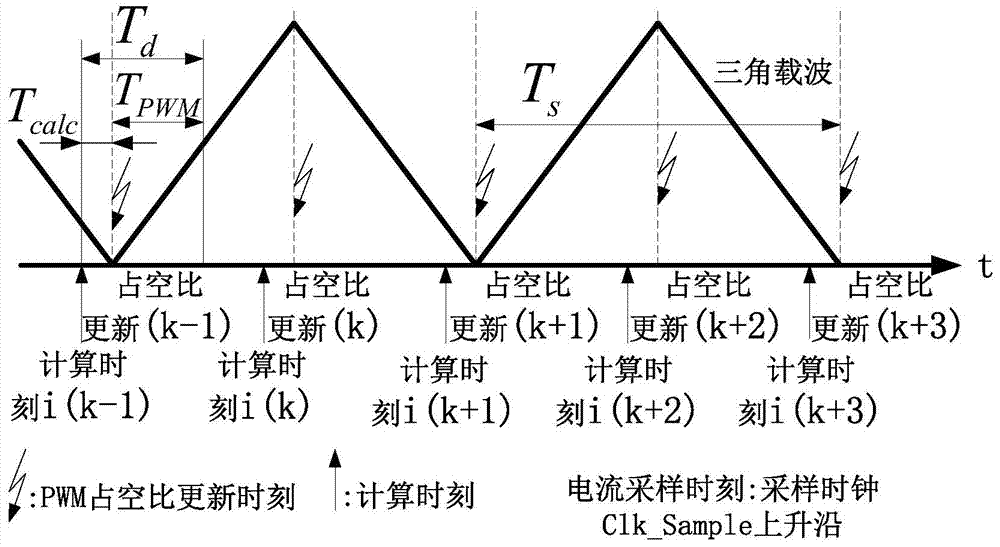

[0034] Such as figure 2 shown, for figure 2 For the current loop control timing diagram of the permanent magnet synchronous motor proposed by the present invention, two vector control calculations and two PWM outputs are performed in one current control cycle, and the current sampling time is adjusted to reduce the delay of the current control loop. Specifically, PWM output is performed a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More