Packaging structure

A technology of packaging structure and plastic sealing layer, which is applied in the direction of electrical components, electric solid devices, circuits, etc., can solve the problems of low packaging efficiency, achieve the effects of improving efficiency, preventing short circuit, and reducing area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

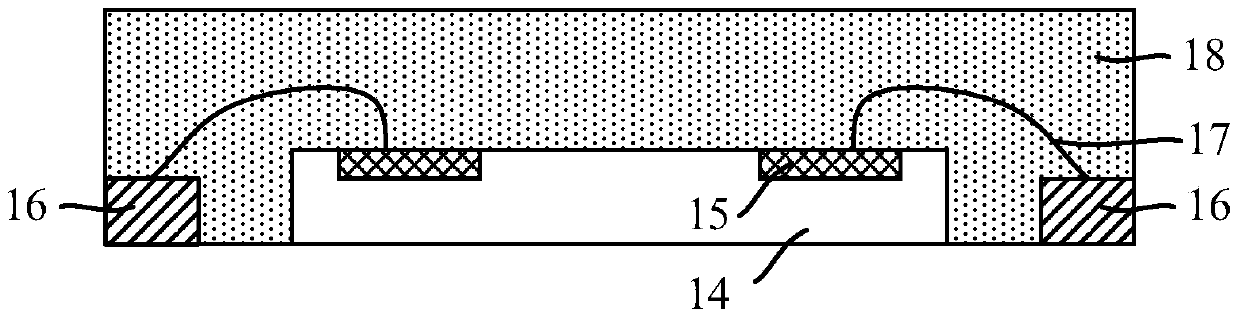

[0024] When encapsulating existing leadframes, please refer to the figure 1 First, the wafer needs to be cut to form semiconductor chips 14 one by one, and then metal wires 17 are formed through a wire bonding process. The metal wires 17 connect the pads 15 on the semiconductor chips 14 with the surrounding pins 16, and finally pass The plastic encapsulation material 18 encapsulates the semiconductor chip 14 and the pin 16. The existing packaging process can only realize the packaging of a single semiconductor chip and pin, and the encapsulation efficiency is low. In addition, the pins 16 are arranged around the semiconductor chip 14, and the pads 15 on the semiconductor chip 14 need to be electrically connected to the surrounding pins 16 through metal wires 17, so that the volume occupied by the entire packaging structure is relatively large. , which is not conducive to the improvement of the integration degree of the packaging structure.

[0025] For this reason, the presen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com