Layout design photoetching technology friendliness detection method based on regular figure filtering

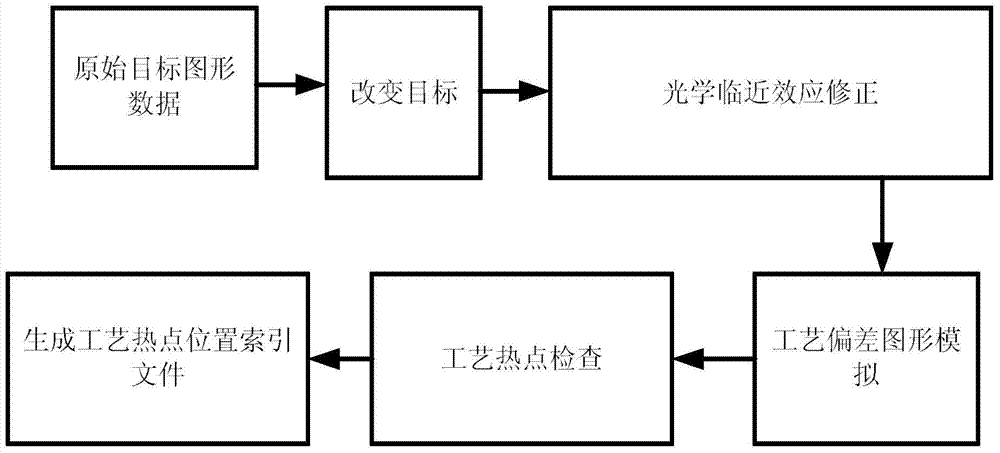

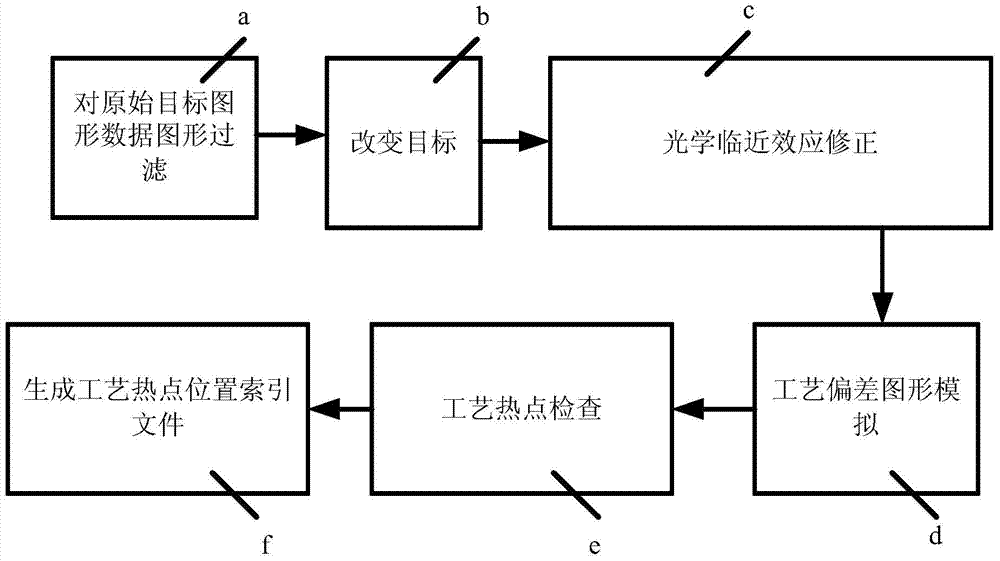

A lithography process and layout design technology, which is applied in the directions of photolithography process exposure devices, microlithography exposure equipment, etc., can solve the problem of long software calculation and use time, unfavorable layout design, lithography process friendliness, application and production cost of inspection kits Advanced problems, to achieve good matching, fast and accurate search, and reduce the cost of use

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

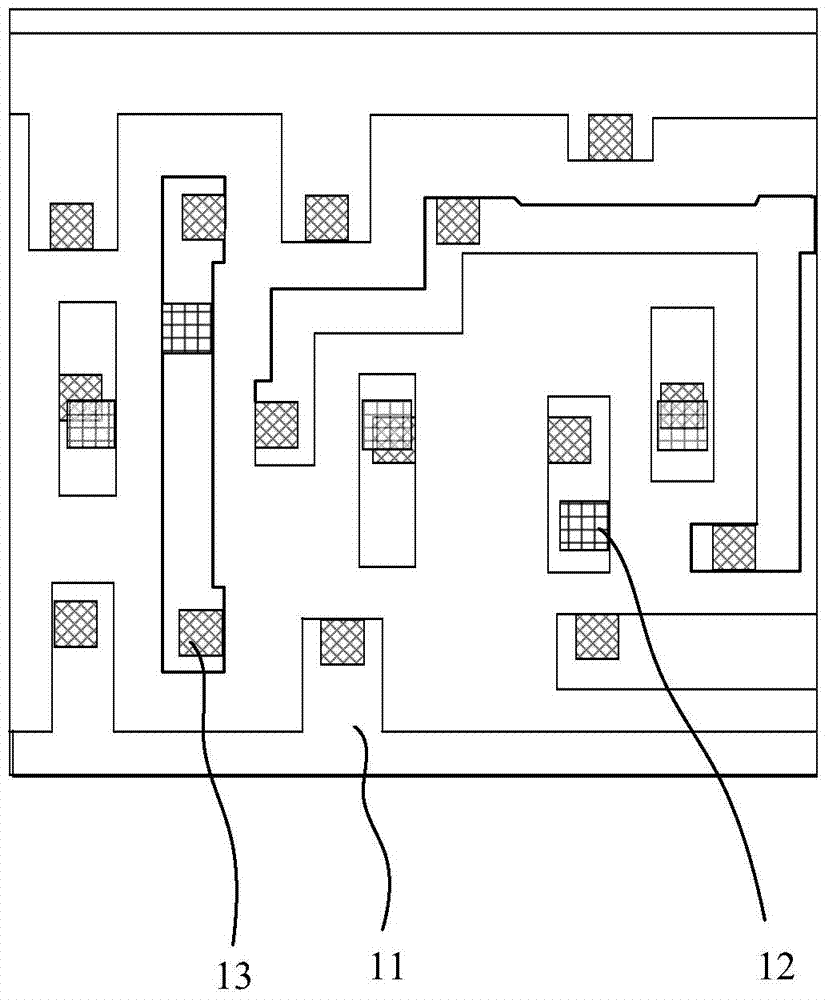

[0044]Figure 3(a) to Figure 3(f) are an embodiment of filtering the original target graphic data in the layout design lithography process friendliness inspection method based on regular graphic filtering according to the present invention, combined with Figure 3(a) to Figure 3 3(f), this embodiment is a method of filtering the original data by using the graphics around the edge fragment near the vertex of the convex angle in the original target graphics data, the filtering method described in this embodiment can be used Look for potential process hotspots such as Line Pinch, Line Bridge, and Hole Overlap Missing.

[0045] For example, filtering raw target pattern data to find potential process hotspots with bad connections. FIG. 3( a ) is a design pattern of part M1 (first metal wiring), including a first connection layer ( M1 ) 11 , a contact hole ( CONTACT ) 12 and a first via layer ( VIA1 ) 13 . As shown in Figure 3(b), select all the cut edges 14 of the convex corner vert...

Embodiment 2

[0047] Figure 4(a) to Figure 4(e) are another embodiment of filtering the original target graphic data in the layout design lithography process friendliness inspection method based on regular graphic filtering according to the present invention, combined with Figure 4(a) ~ Figure 4(e), this embodiment is a method of filtering the original target graphic data by using the graphics around the edge fragment near the concave corner vertex. This method can be used to find Line Pinch and Process hotspots such as Line Bridge.

[0048] FIG. 4( a ) is a design pattern of a small part of M1 (first metal wiring), including the first connection layer 11 (M1). As shown in Figure 4(b), first select all the trimming edges 22 near the vertex of the concave angle, wherein the length of the trimming edges 22 can be 0.5 times the minimum design size of the gap (space), preferably 0.4 to 0.45 times, This keeps two adjacent cut edges from spanning the entire gap width. Then, select the limited s...

Embodiment 3

[0050] Figures 5(a) to 5(g) are yet another embodiment of filtering the original target graphic data in the layout design lithography process friendliness inspection method based on regular graphic filtering according to the present invention, combined with Figure 5(a) ~ Fig. 5(g), this embodiment uses the graph around the edge fragment near the apex of the concave corner to filter the raw data, which can be used to find the channel length of the transistor caused by the short-extended L-shaped design Or a filtering method for the potential process hotspot area of channel width unevenness. This process hot spot will affect the electrical performance of the device or even fail, especially for short-channel transistors.

[0051] FIG. 5( a ) is a plane design of a small part of transistors, including a polycrystalline layer (Poly) 31 and an active area (Active Area) 32 . As shown in FIG. 5( b ), the gate region 33 is selected first, where the width of the active region is calle...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More