Novel packaging method of MEMS (Micro-electromechanical Systems) structure and processing circuit integrated system

A technology for processing circuits and integrated systems, applied in the directions of microstructure devices, manufacturing microstructure devices, circuits, etc. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0049] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

[0050] The novel packaging method of the MEMS structure and processing circuit integrated system of the present invention specifically comprises the following steps:

[0051] Step (1), forming a reserved circuit area 205 on the MEMS wafer

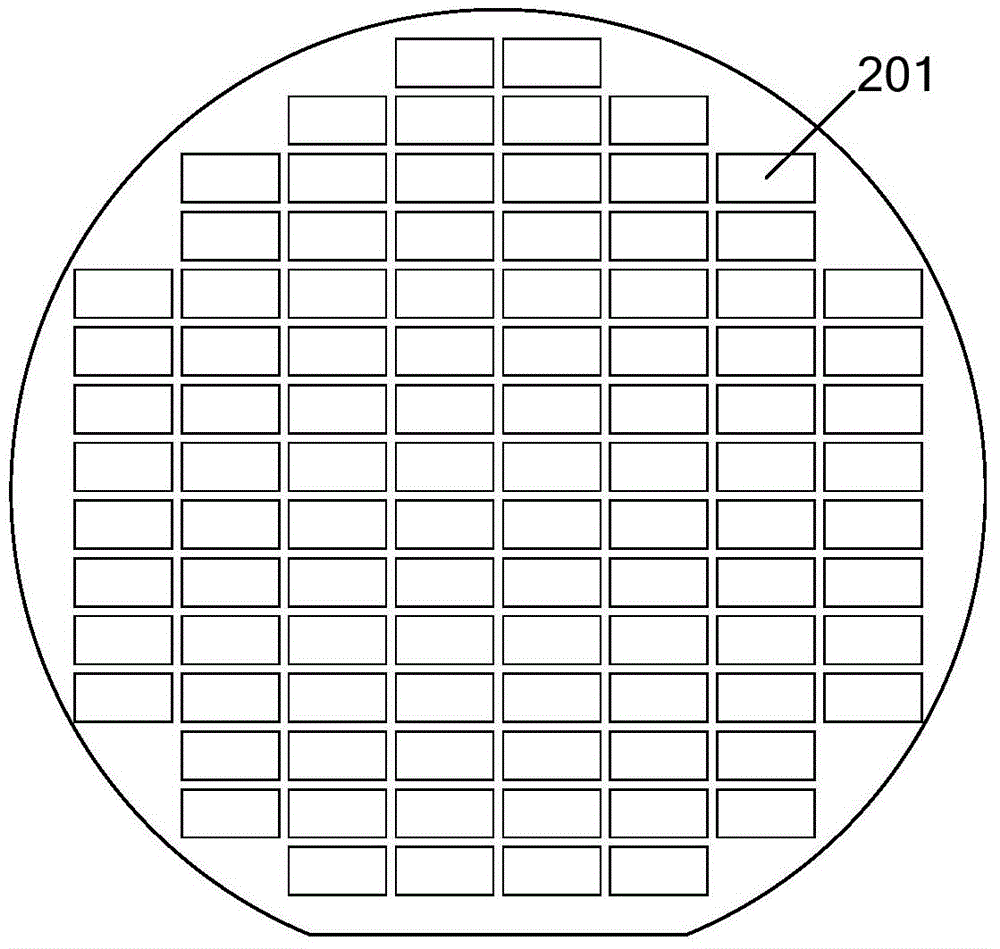

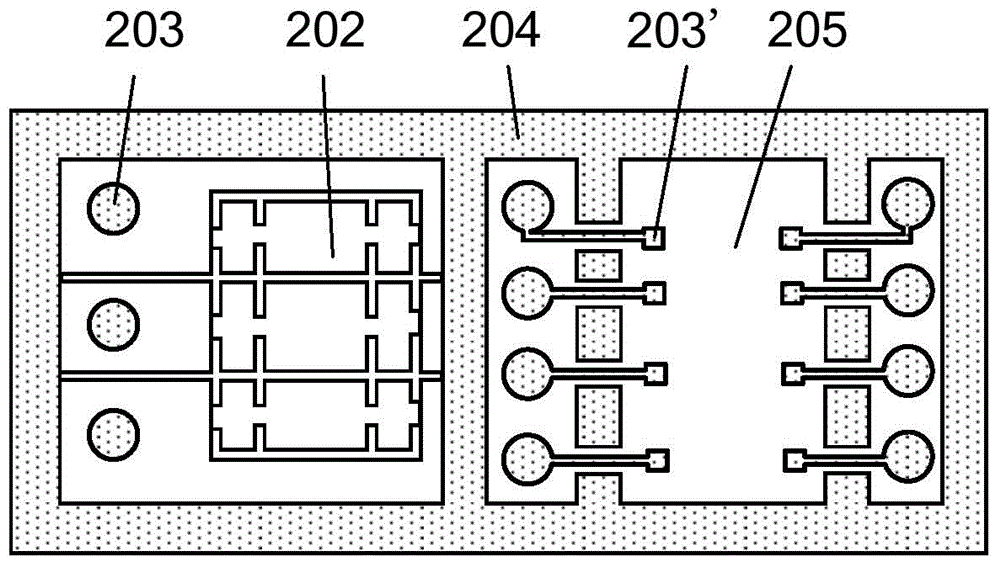

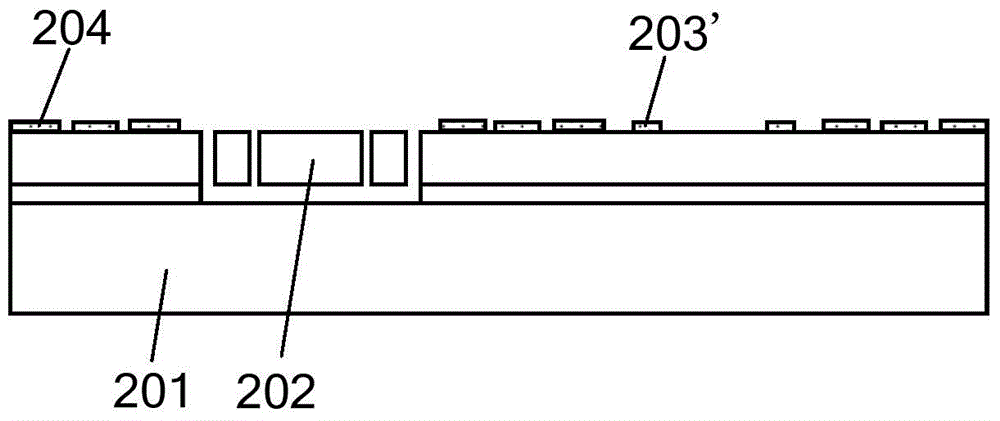

[0052] like figure 1 Shown is a schematic diagram of the distribution of the MEMS wafer before packaging in the present invention. It can be seen from the figure that the MEMS wafer includes N base units. like Figure 2A Shown is a top view of a single MEMS structure on the MEMS wafer before packaging of the present invention, Figure 2B It is a cross-sectional view of a single MEMS structure on a MEMS wafer before packaging in the present invention. On each base unit of the MEMS wafer substrate 201, the MEMS structure 202 is processed by the MEMS process, the metal film layer is formed on the substrate s...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More