Method for reducing stress on peripheral region of silicon through hole

A surrounding area and through-silicon via technology, which is applied in the field of microelectronics, can solve the problems of adverse effects on the normal operation of adjacent devices with service life, great difficulty in technical realization, and complicated process, so as to overcome the complexity of the process and make the process simple and reliable , easy to achieve effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

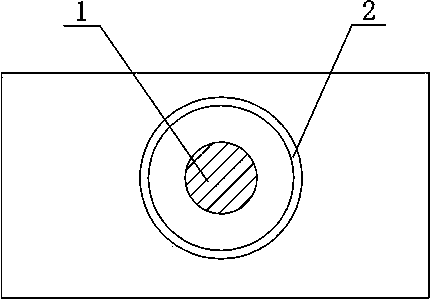

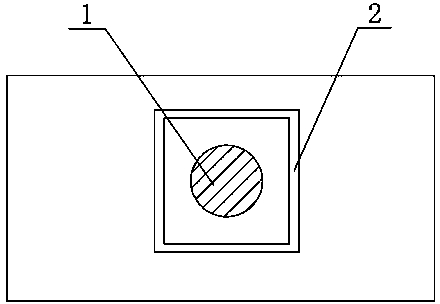

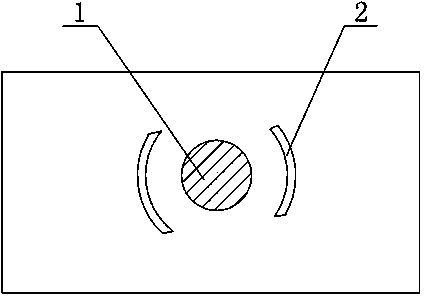

[0021] figure 1 Among them, 1 is a TSV, and 2 is a stress relief structure of an annular groove. The circular ring and the TSV are in a concentric circle structure, but in the actual design process, they may also be non-concentric circles. The distance between the annular groove 2 and the TSV 1 depends on factors such as the diameter and height of the TSV, usually in the range of 0-50 microns, and the depth of the annular groove 2 also depends on factors such as the diameter and height of the TSV , usually in the range of 0-100 microns. This stress relief structure is relatively uniform in stress relief in the area around the TSV, and is suitable for occasions where the device distribution is also relatively uniform. figure 2 and figure 1 Very similar, the difference is that a square groove 2 is used instead of an annular groove. image 3 Among them, 1 is a through-silicon via, and 2 is a stress relief structure of an unclosed arc-shaped groove. The arc-shaped grooves ar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More