Interconnect structure and method of forming the same

A technology of interconnection lines and interlayer dielectric layers, applied in the field of interconnection line structure and its formation, can solve problems such as poor quality, complicated manufacturing process, and large stack thickness, so as to achieve improved quality, low process cost, and reduced Effect of small stack thickness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

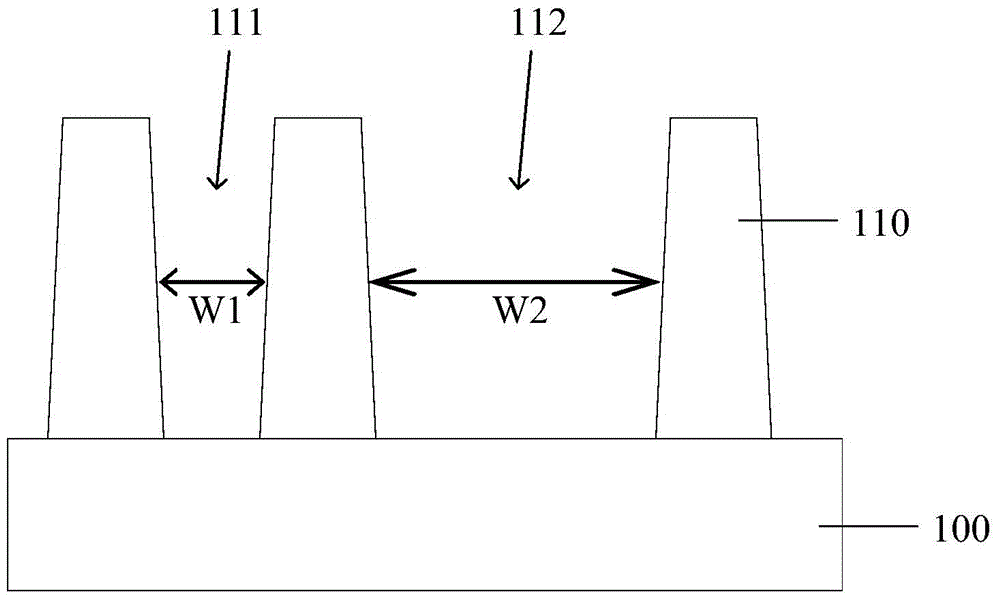

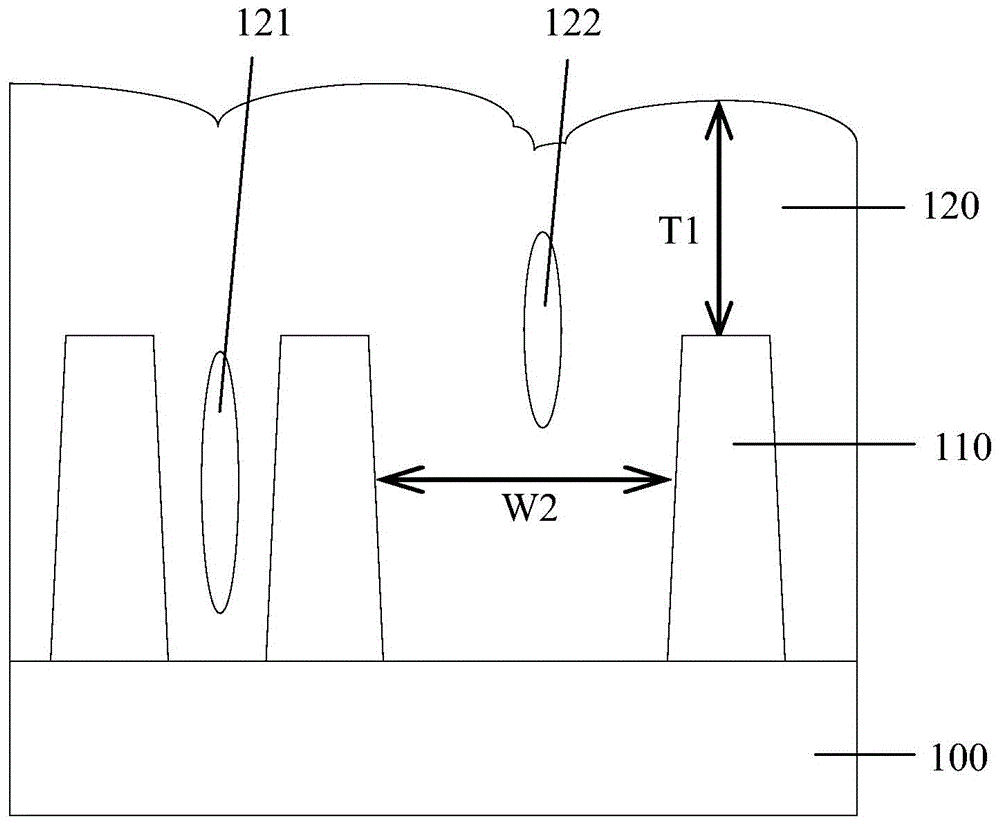

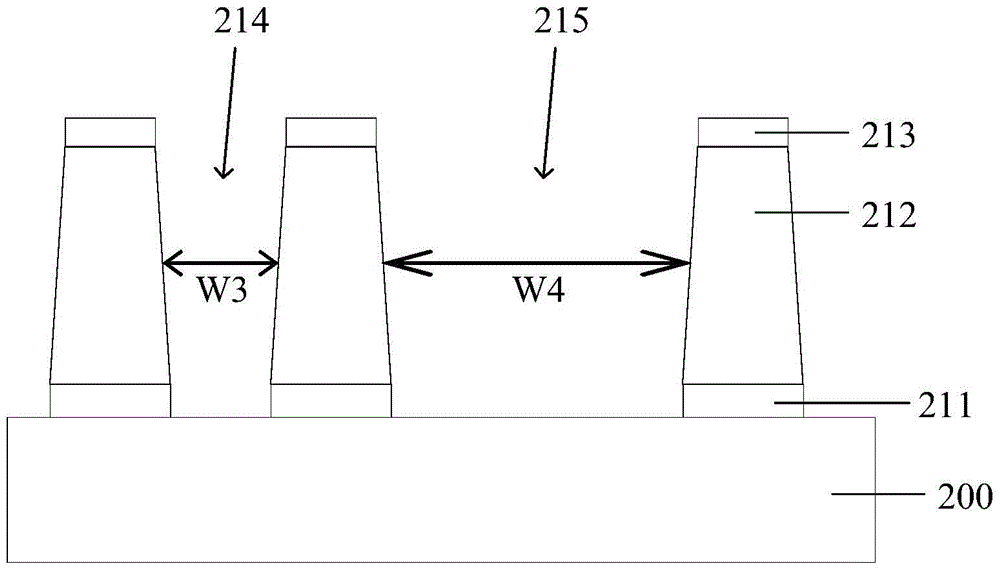

[0039] It can be seen from the description of the background technology that in the existing method for forming the interconnect structure, when the first interlayer dielectric layer is filled with a larger width (for example figure 1 and figure 2 In the case of a trench with a width W2), an air gap at a higher position (relative to the upper surface of the interconnect structure) will be formed. In order to prevent the air gap from causing bubble defects on the upper surface of the interconnect structure, the first interlayer dielectric The thickness of the layer is usually large, and a second interlayer dielectric layer with the same thickness needs to be formed on the first interlayer dielectric layer. In addition, after the second interlayer dielectric layer is planarized, it is also necessary to The protective layer is formed on the dielectric layer, and the whole forming method is complex in process and high in process cost, and the quality of the formed interconnection...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More