Filling method for redundancy graph

A technology of redundant graphics and filling methods, applied in special data processing applications, instruments, electrical digital data processing, etc., to achieve the effects of improving line width uniformity, increasing graphic density, and improving flatness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

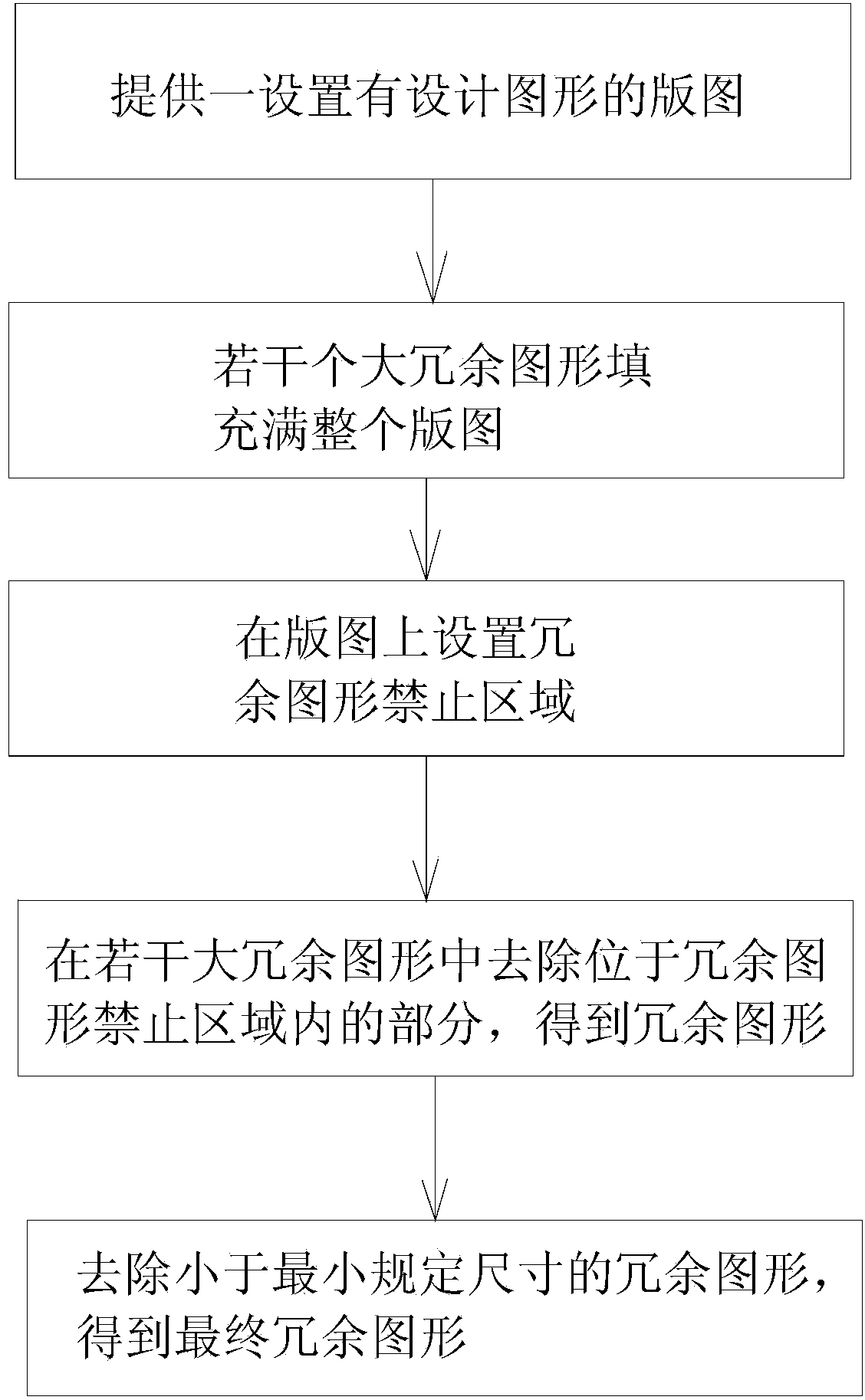

[0040] figure 2 It is the process flow chart of the present invention. The present invention discloses a method for filling redundant graphics, such as figure 2 Shown:

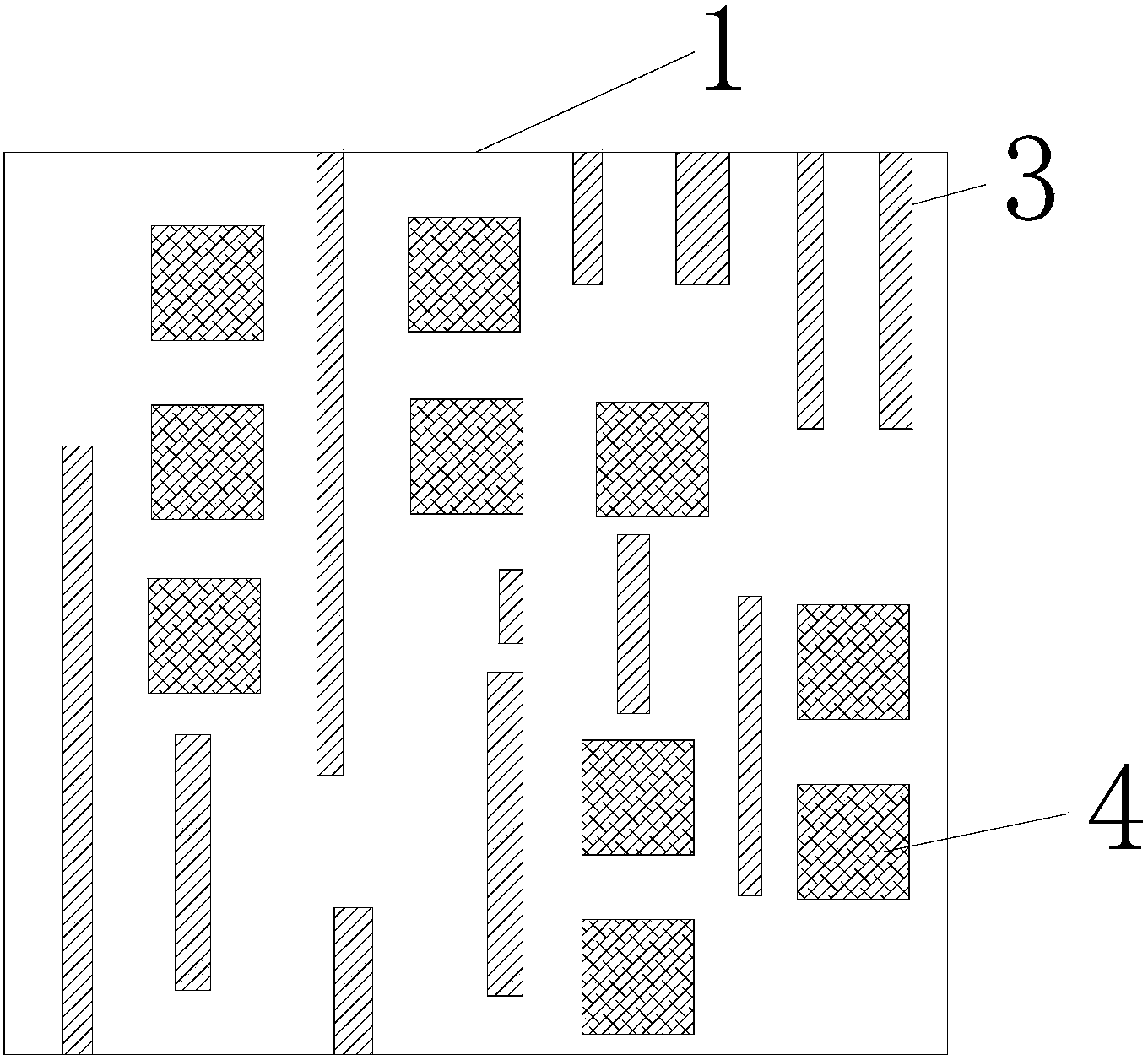

[0041] Step 1: Provide a version with design graphics 3 figure 1 ,Version figure 1 It includes an active layer, a polysilicon layer, a gate layer, and a metal layer. Specifically, an active layer is provided as the lowermost layer of the layout, and the polysilicon layer, the gate layer, and the metal layer are arranged on the active layer from bottom to top. Surface; design graphics 3 are all polygons.

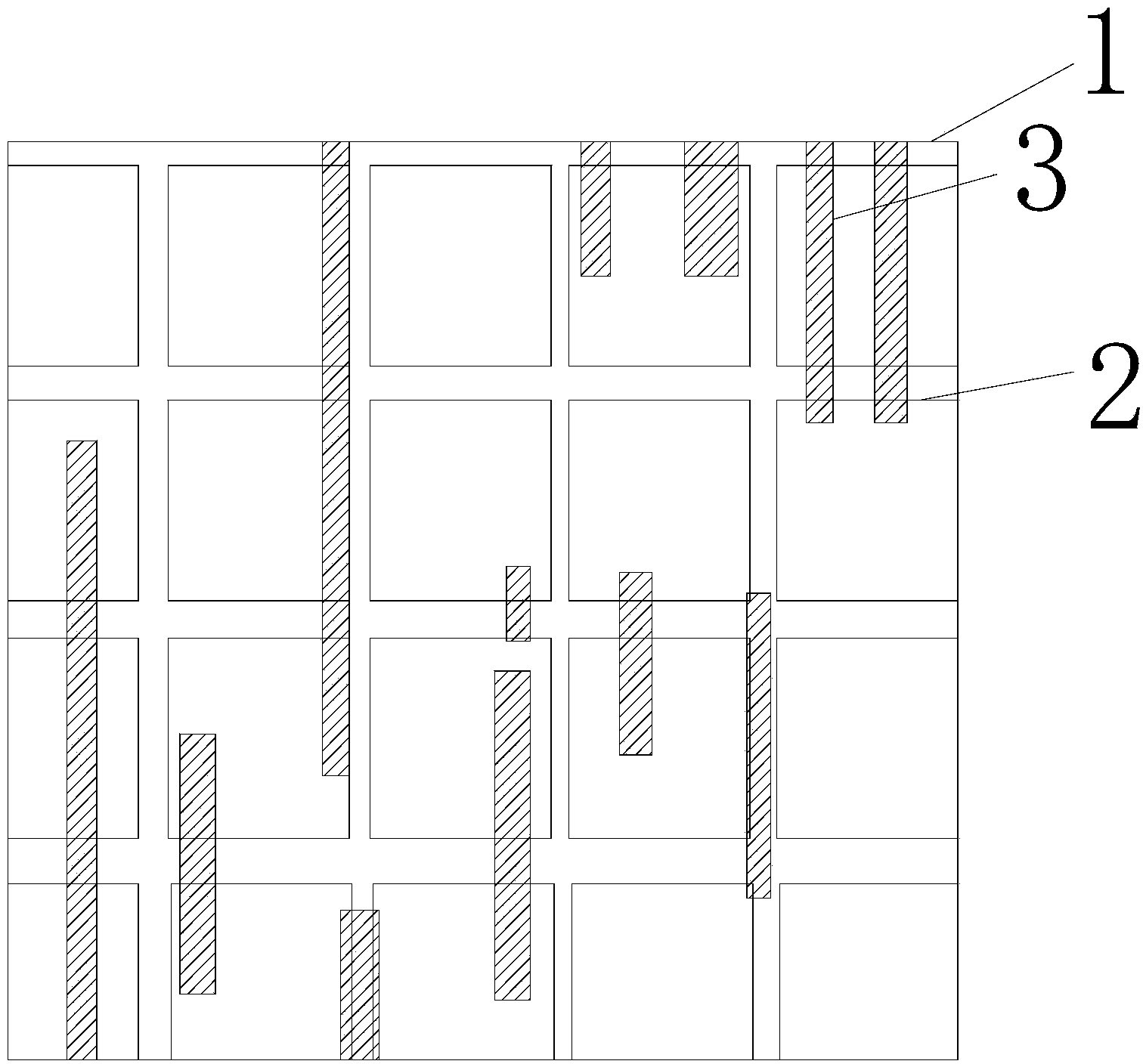

[0042] Step 2: Fill the entire layout with a number of redundant graphics separated by a certain distance from each other. The redundant graphics are polygons. Specifically, the size of the redundant graphics is set by the maximum specified size specified in the layout design rules. Among them, the layout Design rules stipulate various process requirements in layout design (each manufacturer has different layout...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More