Polycrystalline silicon and preparation method thereof

A technology of polysilicon and polysilicon wafers, which is applied in the field of polysilicon and its preparation, can solve the problems of not being able to obtain high-quality complete polysilicon materials, and achieve the effects of less crystal growth dislocation, improved utilization rate, and appropriate grain boundaries

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0026] The method that polysilicon of the present invention prepares adopts, comprises the following steps:

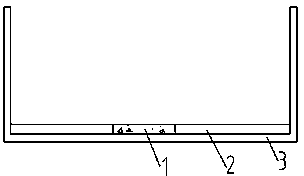

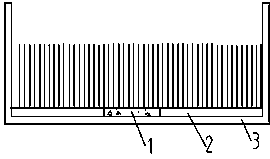

[0027] 1) A number of polysilicon seed crystals are laid in the center of the bottom of the crucible 3 to form a seed layer 1 , the number of polycrystalline seed crystals are closely arranged with each other, and the gap between the several polycrystalline seed crystals is less than 2 mm. Between the seed crystal layer at the bottom of the crucible 3 and the four sides of the crucible, a number of polycrystalline silicon sheets are arranged side by side to form a flat layer 2, and the polycrystalline silicon sheets are scraps of prefabricated polycrystalline silicon ingots. Wherein, the seed crystal layer 1 is arranged in the center of the bottom of the crucible in a square shape, and the cross section of the bottom of the crucible is square; the flat layer 2 adopts a square polysilicon wafer of the same size. When laying, ensure that the seed layer 1 and the paving l...

Embodiment 2

[0031] The method that polysilicon of the present invention prepares adopts, comprises the following steps:

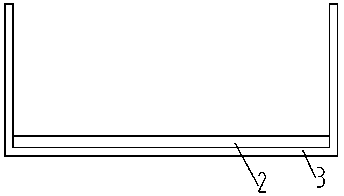

[0032] 1) On the bottom of the crucible 3, a number of polycrystalline silicon wafers are arranged side by side to form a flat layer 2, and the polycrystalline silicon wafers are scraps of prefabricated polycrystalline silicon ingots. Wherein, the tiled layer 2 adopts rectangular polysilicon wafers of the same size and specification, and the thickness of the tiled layer is between 20 mm and 50 mm.

[0033] 2) The silicon material in a molten state is arranged on the flat layer 2 to ensure that the heating temperature at the bottom of the crucible 3 is lower than the melting point of the polysilicon wafer, so that the thickness of the flat layer after the silicon material is melted is equal to that of the pre-laid flat layer 2 1 / 4~1 / 2 of the thickness; among them, the silicon material is solid silicon material, and the temperature in the upper part of the crucible is gu...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More