Preparation method of punch-through silicon carbide insulated gate bipolar transistor

A technology of bipolar transistor and general-type silicon carbide, which is applied in the field of microelectronics, can solve the problems of high production cost, high energy consumption in the epitaxial process, and high process requirements, so as to save resources and energy, reduce the difficulty of preparation, and save the cost of preparation effect with time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

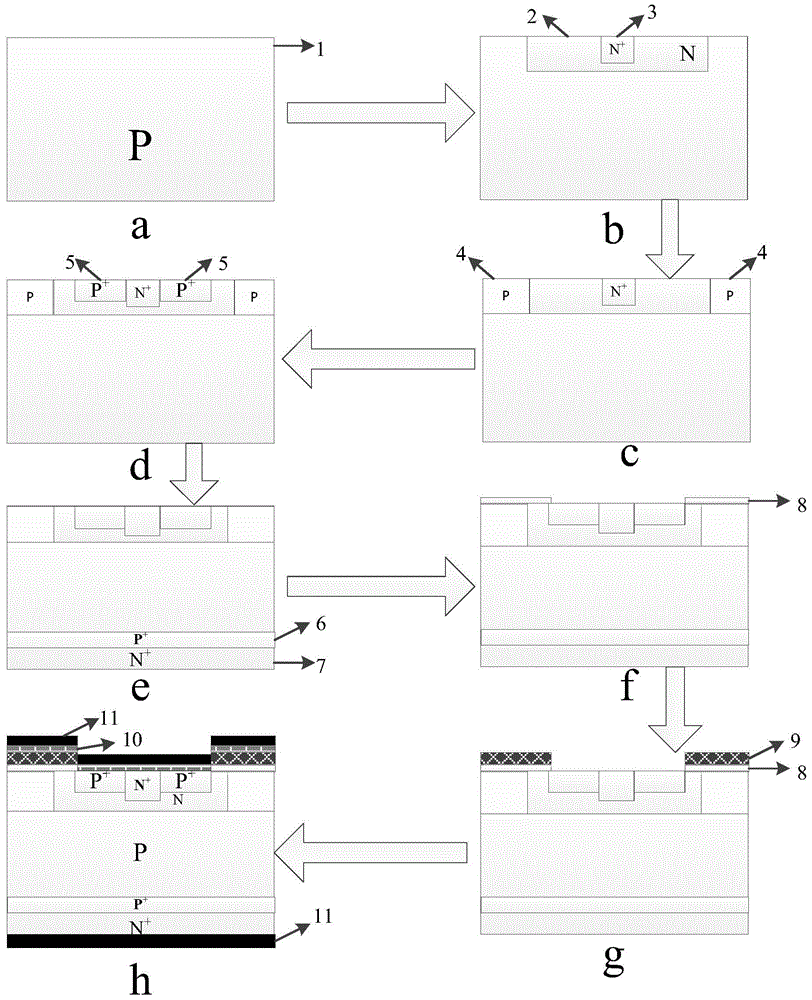

[0030] Example 1: The dislocation density at the base plane is 10 4 / cm 2 , the substrate concentration is 2×10 14 cm -3 A punch-through silicon carbide insulated gate bipolar transistor was fabricated on a P-type SiC substrate without a micropipe structure.

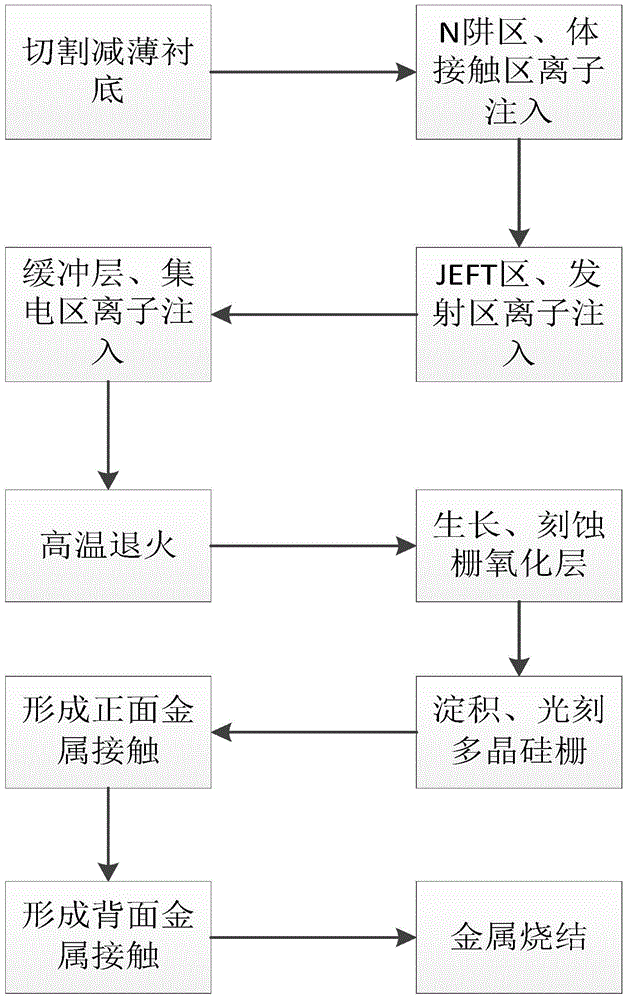

[0031] refer to figure 1 and figure 2 , the implementation steps of this embodiment are as follows:

[0032] Step 1: Substrate processing.

[0033] Cutting and thinning to 100 μm along the back side of the P-type SiC substrate 1, such as figure 2 a; Polish the cutting surface, then wet oxygen oxidation at 950°C for 20 minutes, then remove the oxide layer, and restore the structure and flatness of the cutting surface.

[0034] Step 2: N well ion implantation.

[0035] (2.1) Deposit a layer of SiO with a thickness of 0.2 μm on the front of the P-type SiC substrate by low-pressure chemical vapor deposition 2 , and then deposit Al with a thickness of 1 μm as a barrier layer for nitrogen ion implantation, and apply...

Embodiment 2

[0059] Example 2: The dislocation density at the base plane is 10 4 / cm 2 , the substrate concentration is 6×10 14 cm -3 A punch-through silicon carbide insulated gate bipolar transistor was fabricated on a P-type SiC substrate without a micropipe structure.

[0060] refer to figure 1 and figure 2 , the implementation steps of this embodiment are as follows:

[0061] Step A: Same as Step 1 of Example 1.

[0062] Step B: N-well implantation.

[0063] (b1) is identical with the step (2.1) of embodiment 1;

[0064] (b2) Perform two ion implantations on the front side of the P-type SiC substrate at 650°C, that is, first use 450Kev implantation energy, 5×10 12 cm -2 Implantation dose of nitrogen ion implantation, and then use the implantation energy of 250Kev, 1 × 10 12 cm -2 Implantation dose of the second nitrogen ion implantation, forming N well 2, such as figure 2 b.

[0065] Step C: Apply glue on the front side of the P-type SiC substrate that has completed the ...

Embodiment 3

[0079] Example 3: The dislocation density at the base plane is 10 4 / cm 2 , the substrate concentration is 1×10 15 cm -3 A punch-through silicon carbide insulated gate bipolar transistor was fabricated on a P-type SiC substrate without a micropipe structure.

[0080] refer to figure 1 and figure 2 , the implementation steps of this embodiment are as follows:

[0081] The first step: same as step 1 of embodiment 1.

[0082] Step 2: Deposit a layer of SiO with a thickness of 0.2 μm on the front side of the P-type SiC substrate by low-pressure chemical vapor deposition 2 , and then deposit Al with a thickness of 1 μm as a barrier layer for nitrogen ion implantation, and apply glue to photoetch the window of the N well implantation region; perform two ion implantations on the front side of the P-type SiC substrate at 650 ° C, that is, first use 600Kev Inject energy, 8×10 12 cm -2 Implantation dose of nitrogen ion implantation, and then using the implantation energy of 35...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More