Method for manufacturing N-channel silicon carbide insulated gate bipolar transistor

A bipolar transistor and silicon carbide technology, applied in the field of microelectronics, can solve the problems of high manufacturing cost, high energy consumption in the epitaxy process, and large on-resistance, so as to save resources and energy, reduce the difficulty of preparation, and save the cost of preparation effect with time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

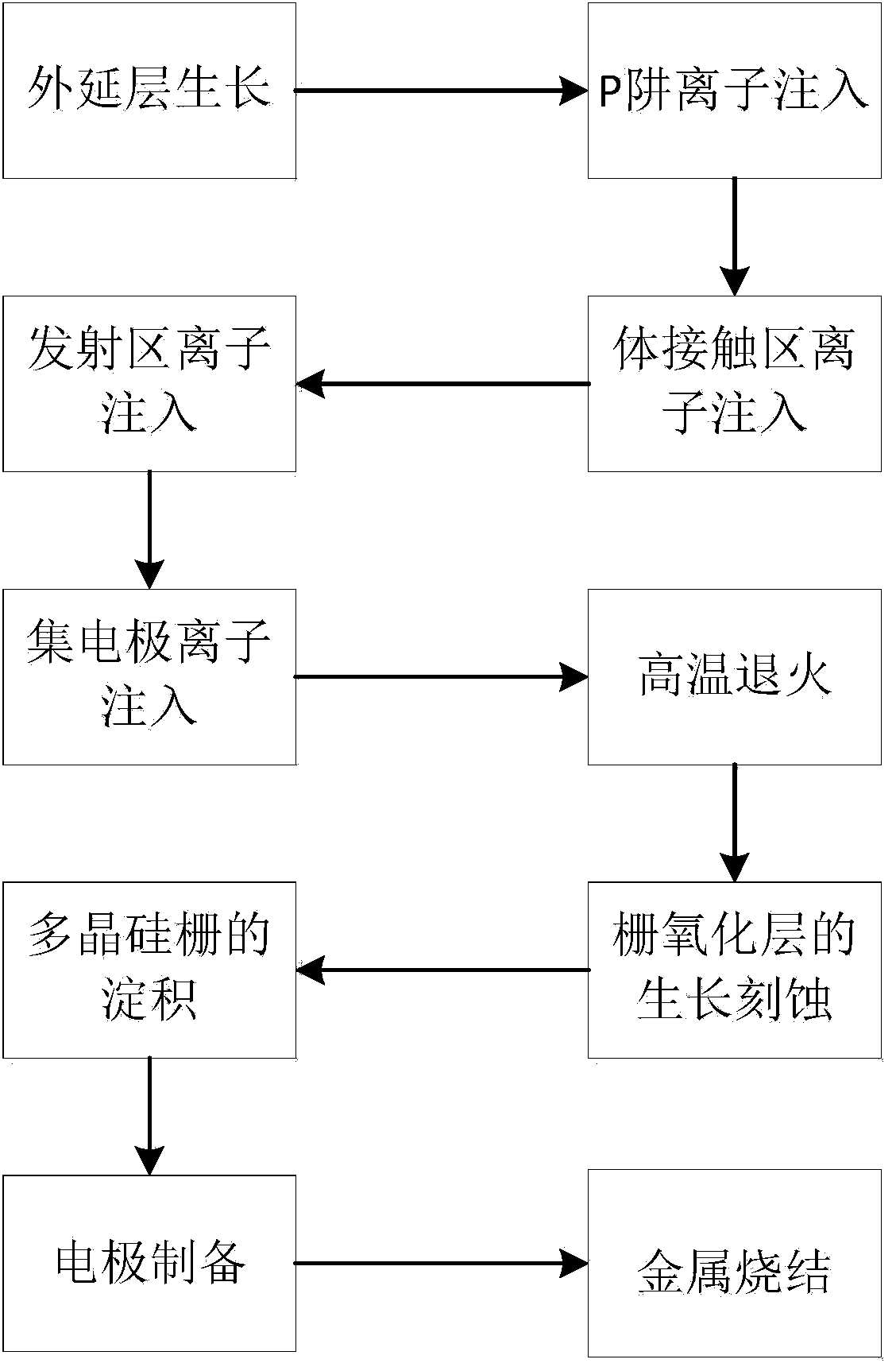

Method used

Image

Examples

Embodiment 1

[0030] Example 1: Dislocations in the base plane are 10 4 / cm -3 , the substrate concentration is 2×10 14 cm -3 N-channel silicon carbide insulated gate bipolar transistors were prepared on the micropipe-free N-type SiC substrate.

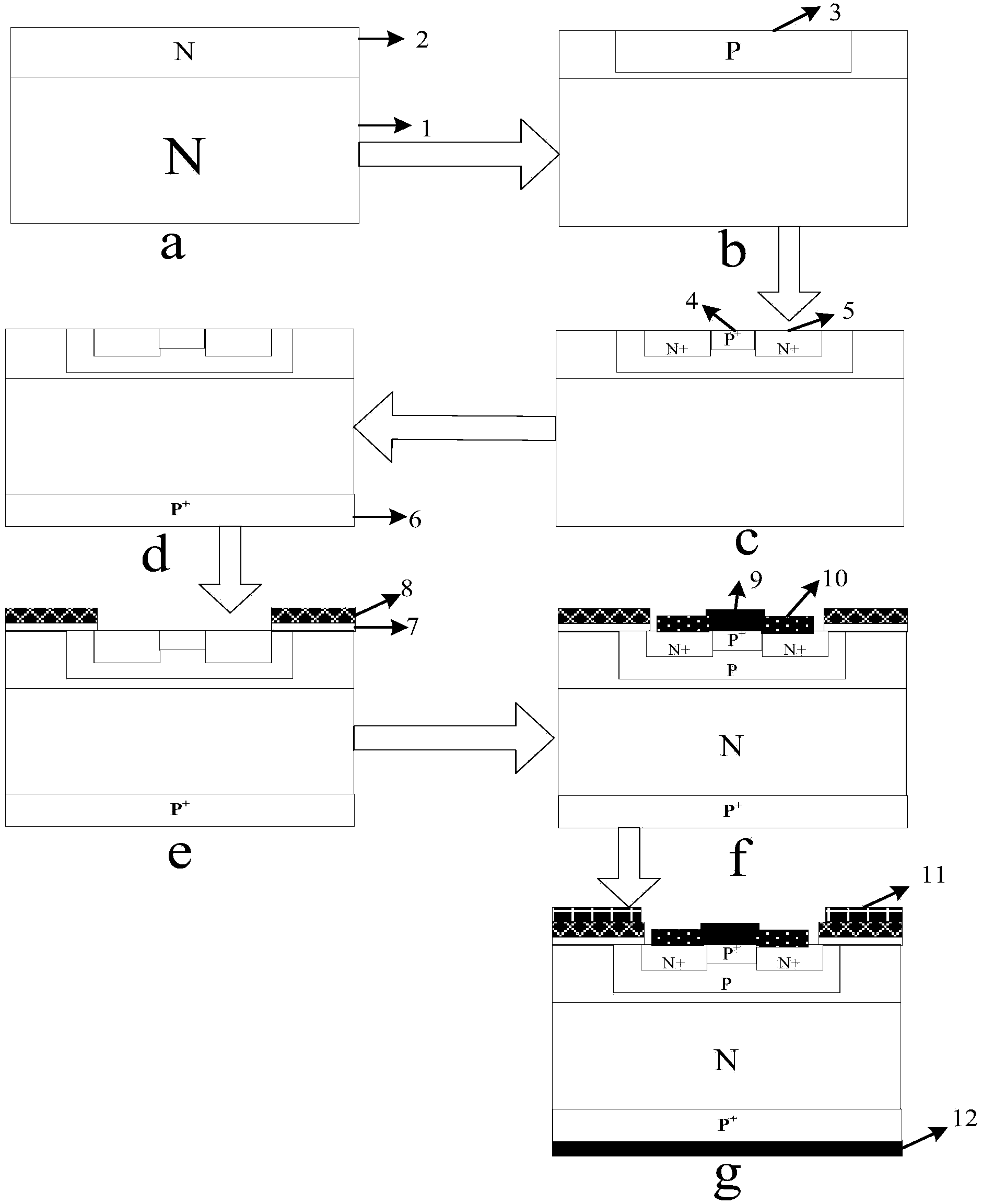

[0031] Step 1: grow epitaxial layer.

[0032] First perform RCA standard cleaning on the N-type silicon carbide substrate 1, and then epitaxially grow on the entire substrate with a thickness of 0.8 μm and a nitrogen ion doping concentration of 2×10 15 cm -3 N-type epitaxial layer 2, such as image 3 a, The epitaxy process conditions are: temperature 1600°C, pressure 100mbar, silane and propane as reaction gas, pure hydrogen as carrier gas, and liquid nitrogen as dopant source.

[0033] Step 2: P well implantation.

[0034] (2.1) Deposit Al with a thickness of 1.5 μm on the entire silicon carbide epitaxial layer by low-pressure chemical vapor deposition as a barrier layer for P-well ion implantation, and then apply glue and photoetch the P-w...

Embodiment 2

[0057] Example 2: Dislocations in the base plane are 10 4 / cm -3 , the substrate concentration is 3×10 14 cm -3 N-channel silicon carbide insulated gate bipolar transistors were prepared on the micropipe-free N-type SiC substrate.

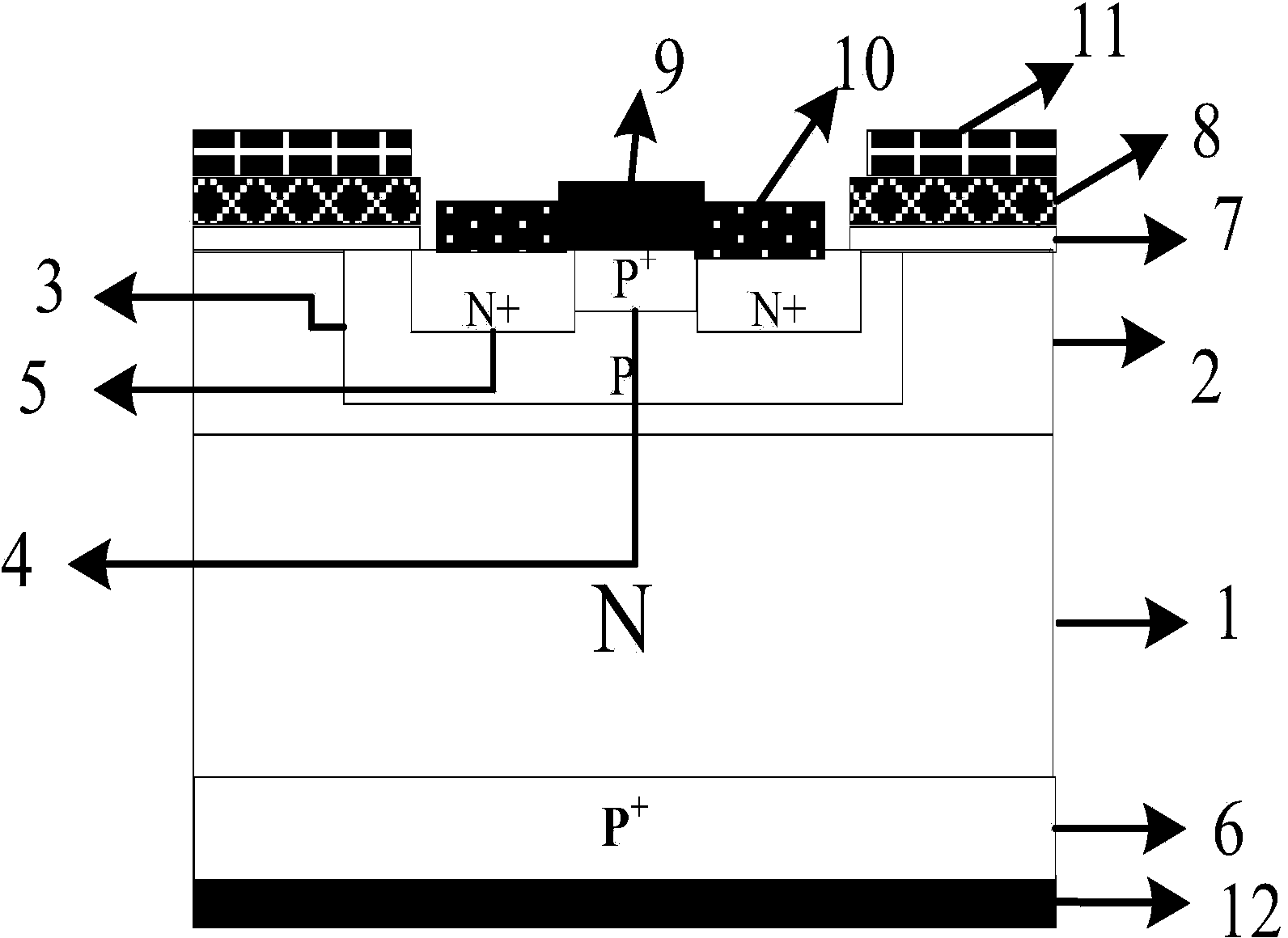

[0058] refer to figure 1 and figure 2 , the implementation steps of this embodiment are as follows:

[0059] Step 1: RCA standard cleaning is performed on the N-type SiC substrate 1 first, and the epitaxial growth thickness on the entire substrate is 1 μm, and the nitrogen ion doping concentration is 5×10 15 cm -3 N-type epitaxial layer 2, such as image 3 a. The process conditions are as follows: temperature is 1600°C, pressure is 100mbar, silane and propane are used as reaction gas, pure hydrogen is used as carrier gas, and liquid nitrogen is used as dopant source.

[0060] The second step: P well injection.

[0061] The specific implementation of this step is the same as step 2 of embodiment 1.

[0062] The third step: apply glue on t...

Embodiment 3

[0072] Dislocations in the basal plane are 10 4 / cm -3 , the substrate concentration is 5×10 14 cm -3 N-channel silicon carbide insulated gate bipolar transistors were prepared on the micropipe-free N-type SiC substrate.

[0073] refer to figure 1 and figure 2 , the implementation steps of this embodiment are as follows:

[0074] Step A: epitaxial layer growth.

[0075] First perform RCA standard cleaning on the N-type silicon carbide substrate 1, and then epitaxially grow the entire substrate with a thickness of 1.4 μm and a nitrogen ion doping concentration of 7×10 15 cm -3 N-type epitaxial layer 2, such as image 3 a, The epitaxy process conditions are: temperature 1600°C, pressure 100mbar, silane and propane as reaction gas, pure hydrogen as carrier gas, and liquid nitrogen as dopant source.

[0076] Step B: P-well implantation.

[0077] The specific implementation of this step is the same as step 2 of embodiment 1.

[0078] Step C: P + Body contact area injec...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More