Preparation method of silicon carbide insulated gate bipolar transistor

A technology of bipolar transistors and insulated gates, which is applied in the fields of inverters, lighting circuits and motors, microelectronics, switching power supplies, and frequency converters. Achieve the effects of saving preparation cost and time, reducing preparation difficulty, saving resources and energy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0025] Example 1: Dislocations in the base plane are 10 4 / cm -3 , the substrate concentration is 2×10 14 cm -3 Silicon carbide insulated gate bipolar transistors were prepared on the micropipe-free P-type SiC substrate.

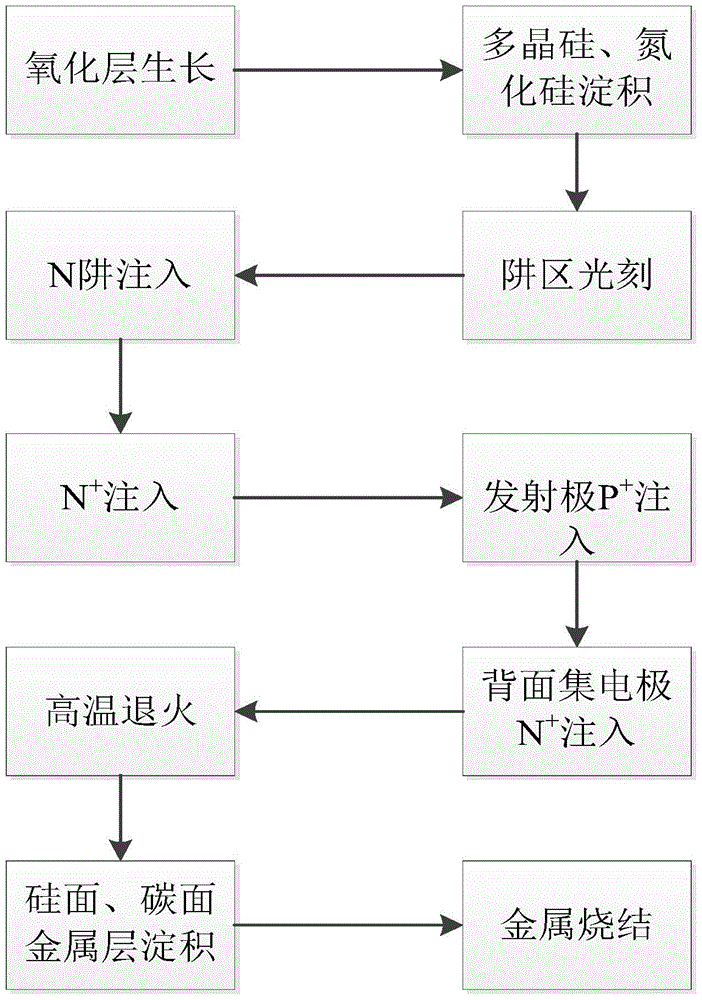

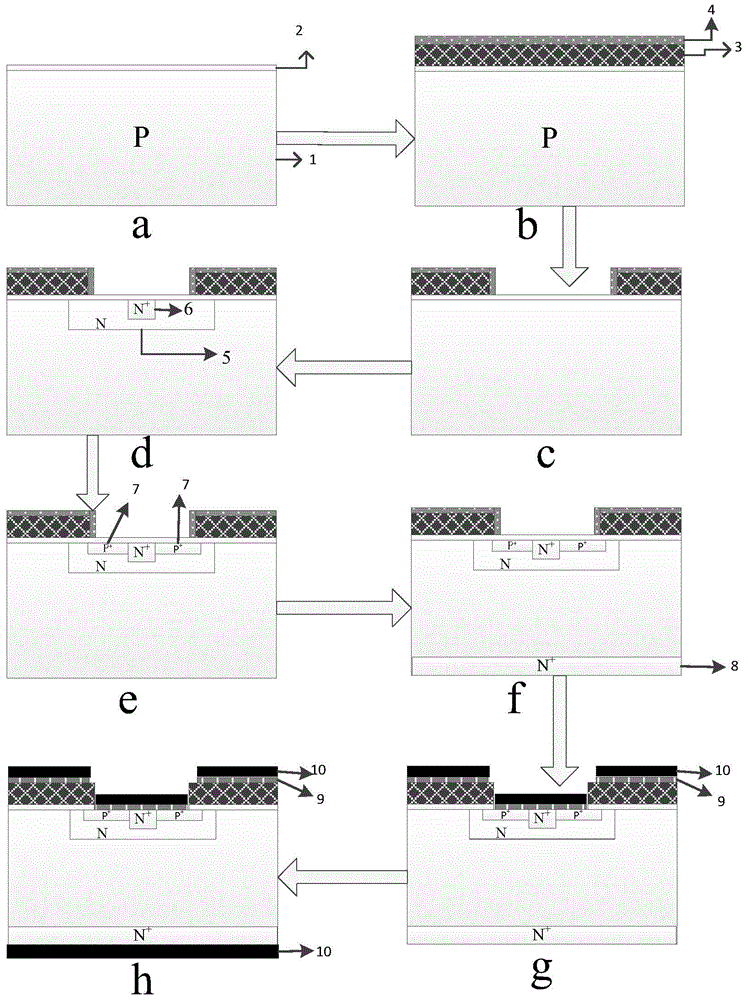

[0026] refer to figure 1 with figure 2 , the implementation steps of this embodiment are as follows:

[0027] Step 1: growing an oxide layer on the silicon surface.

[0028] First dry oxygen oxidation on the silicon surface of the substrate at 1200°C for one hour, and then wet oxygen oxidation at 950°C for one hour to form an oxide layer 2 with a thickness of 50nm on the silicon surface of the substrate, as figure 2 a; then at 1050°C in N 2 Annealing under atmosphere to reduce SiO 2 The roughness of the film surface.

[0029] Step 2: Deposit polysilicon.

[0030] On the oxide layer, a polysilicon 3 with a thickness of 2 μm and a silicon nitride protective layer 4 with a thickness of 100 nm were sequentially deposited by the low-pressure chemical ...

Embodiment 2

[0047] Dislocations in the basal plane are 10 4 / cm -3 , the substrate concentration is 6×10 14 cm -3 Silicon carbide insulated gate bipolar transistors were prepared on the micropipe-free P-type SiC substrate.

[0048] refer to figure 1 with figure 2 , the implementation steps of this embodiment are as follows:

[0049] Step A: growing an oxide layer on the silicon surface.

[0050] Dry oxygen oxidation at 1200°C for 2 hours, and then wet oxygen oxidation at 950°C for one hour to form an oxide layer 2 with a thickness of 70nm, as figure 2 a; then at 1050°C in N 2 Annealing under atmosphere to reduce SiO 2 The roughness of the film surface.

[0051] Step B: Deposit polysilicon.

[0052] On the oxide layer, a low-pressure chemical vapor deposition method is used to deposit polysilicon 3 with a thickness of 4 μm and a silicon nitride protective layer 4 with a thickness of 100 nm at a deposition pressure of 220 Pa and a deposition temperature of 650 ° C, such as fig...

Embodiment 3

[0066] Dislocations in the basal plane are 10 4 / cm -3 , the substrate concentration is 1×10 15 cm -3 Silicon carbide insulated gate bipolar transistors were prepared on the micropipe-free P-type SiC substrate.

[0067] refer to figure 1 with figure 2 , the implementation steps of this embodiment are as follows:

[0068] Step 1: grow the oxide layer on the silicon surface, that is, dry oxygen oxidation on the silicon surface of the substrate at 1200°C for 3 hours, and then wet oxygen oxidation at 950°C for 90 minutes to form an oxide layer with a thickness of 100nm on the silicon surface of the substrate. Layer 2, such as figure 2 a; then at 1050°C in N 2 Annealing under atmosphere to reduce SiO 2 The roughness of the film surface.

[0069] Step 2: On the oxide layer, the polysilicon 3 and the silicon nitride protective layer 4 are sequentially deposited by low-pressure chemical vapor deposition method, and the conditions are as follows: deposition pressure 300Pa, d...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More