Thin film transistor array substrate, manufacturing method and liquid crystal display panel

A technology of thin film transistors and array substrates, which is applied in the field of liquid crystal display, and can solve problems such as lowered display quality of liquid crystal display panels, uneven color of liquid crystal display panels, and image deformation.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

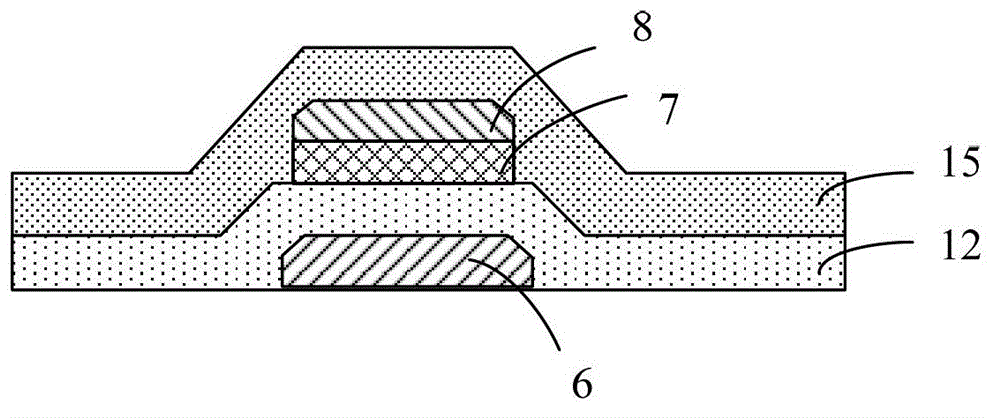

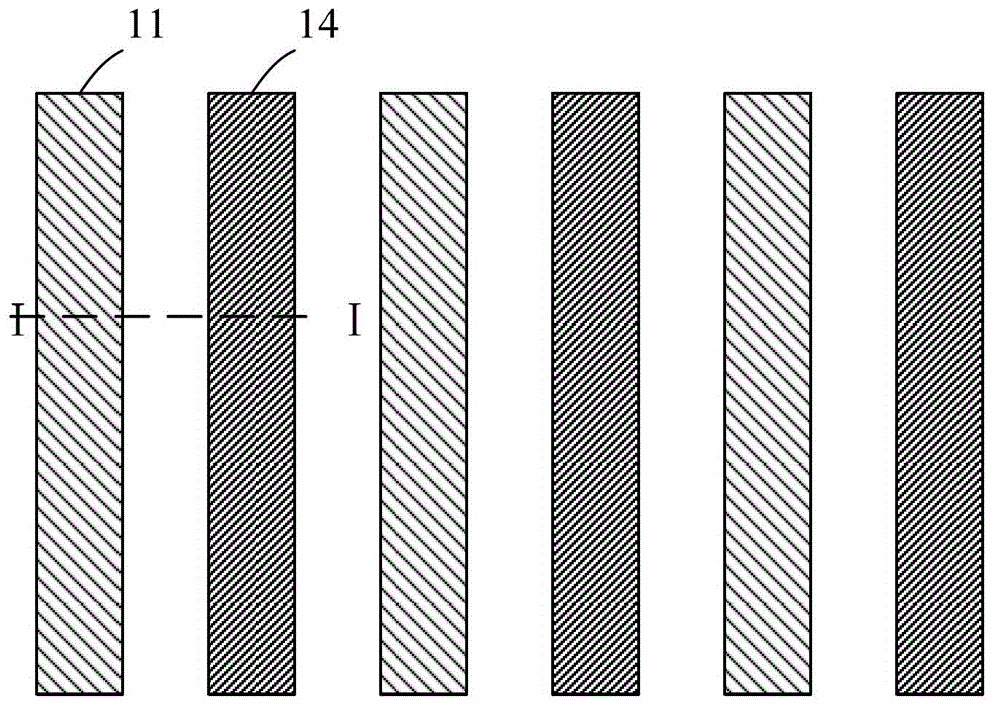

[0047] The data line leads are divided into a plurality of first data line leads located under the insulating layer and a plurality of second data line leads located on the insulating layer that do not overlap with the positions of the first data lead wires; The wire lead is composed of a first metal layer, and the second data line lead is composed of a second metal layer; the lead film layer at the position of the second data line lead includes the first sub-increasing layer, the second sub-increasing layer .

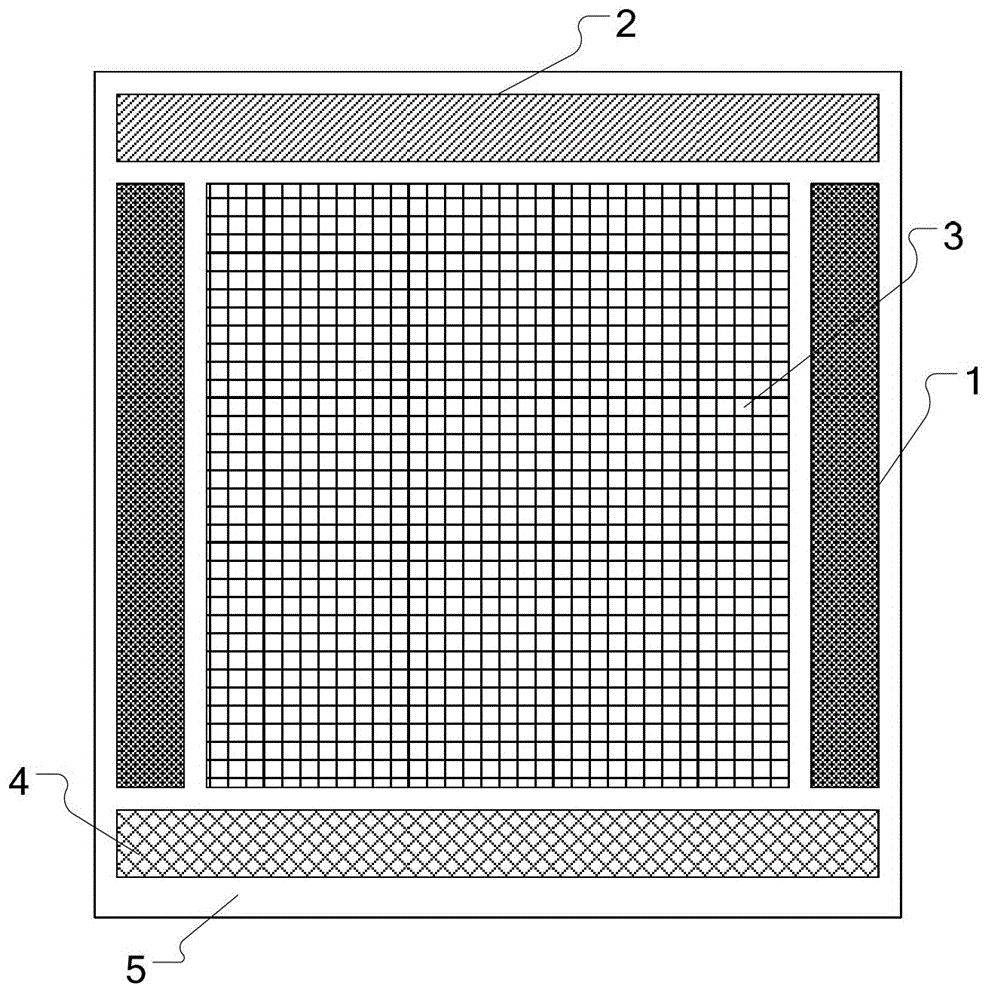

[0048] refer to Figure 8 , Figure 8 It is a schematic cross-sectional view of the film layer of the data line lead area 4 in the first embodiment of the present invention. The array substrate of the liquid crystal display device provided by the present invention includes a plurality of first data line leads 11 and second data line leads 14 arranged at intervals along the same direction, such as image 3 As shown, the distance between the leads of two adjacent data...

no. 2 example

[0059] The thin film transistor array substrate also includes a common electrode line lead area, and the common electrode line is divided into a plurality of first common electrode line leads located under the insulating layer and a plurality of second common electrodes located on the insulating layer Wire. The first common electrode lead is made of a first metal layer, and the second common electrode lead is made of a second metal layer. On the basis of the first embodiment, a booster layer can also be provided at the lead of the first common electrode line to achieve the purpose of reducing the difference in film layer height on the non-display area around the array substrate. The lead film layer where the first common electrode lead 9 is located includes a third sub-buildup layer and a fourth sub-buildup layer.

[0060] refer to Figure 10 , Figure 10 It is a schematic cross-sectional view of the film layer in the lead area 2 of the common electrode line in the second e...

no. 3 example

[0070] The thin film transistor array substrate also includes a common electrode line lead area, and the common electrode line is divided into a plurality of first common electrode line leads located under the insulating layer and a plurality of second common electrodes located on the insulating layer Wire. The first common electrode lead is made of a first metal layer, and the second common electrode lead is made of a second metal layer. On the basis of the first embodiment, a booster layer can also be provided at the lead of the second common electrode line to achieve the purpose of reducing the difference in film layer height on the non-display area around the array substrate. The lead film layer where the first common electrode lead 9 is located includes a fifth sub-buildup layer and a sixth sub-buildup layer.

[0071] refer to Figure 11 , Figure 11 It is a schematic cross-sectional view of the film layer in the lead area 2 of the common electrode line in the third em...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Film thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More