Shift register unit, gate drive circuit and display device

A shift register and gate technology, applied in static memory, digital memory information, instruments, etc., can solve the problem that the shift register unit cannot realize bidirectional scanning, the time for the fourth transistor to apply a high level is short, and the brightness of the display device is not high. Equalize problems to achieve the effect of increasing achievability, reducing erroneous output, and simplifying structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

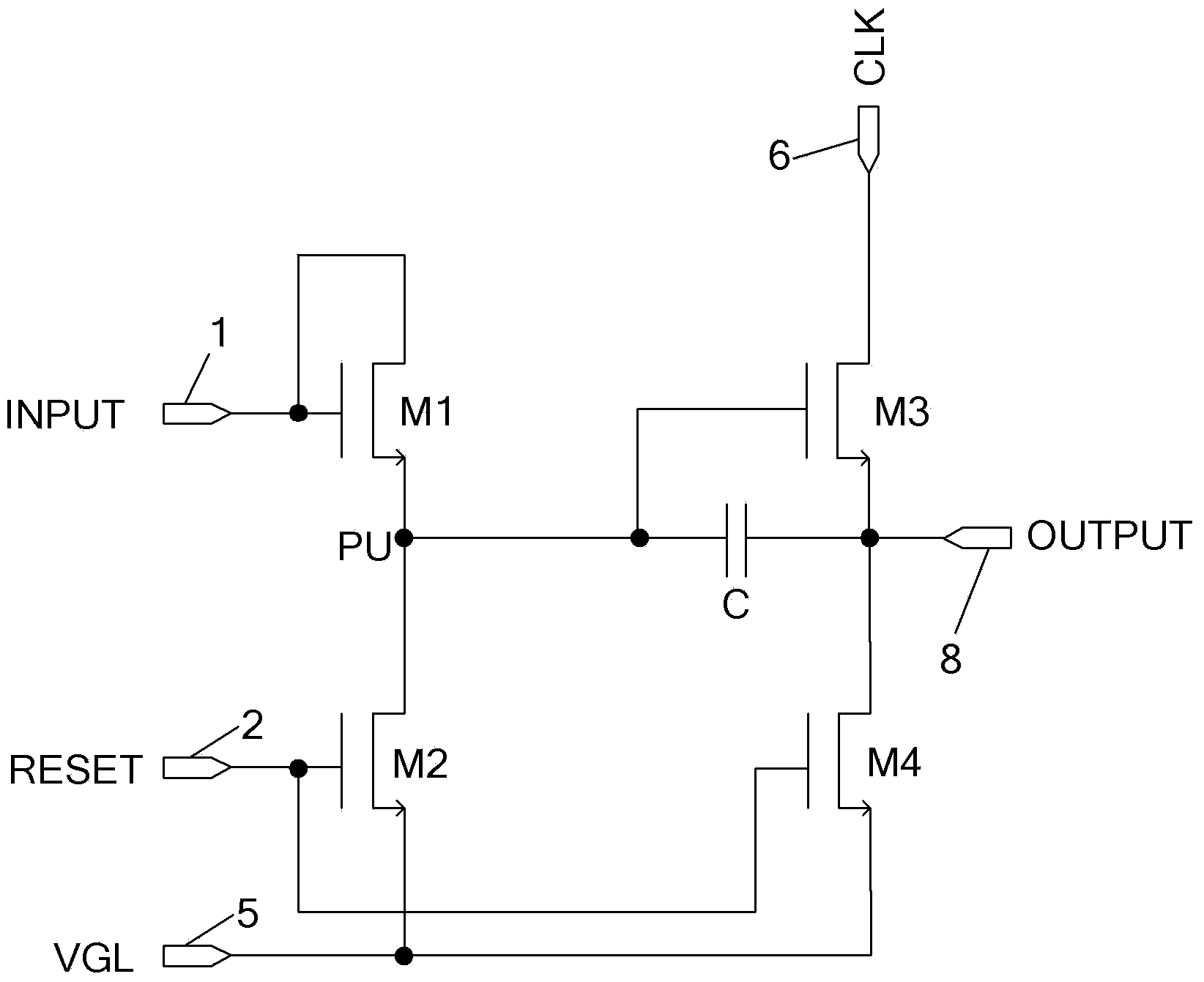

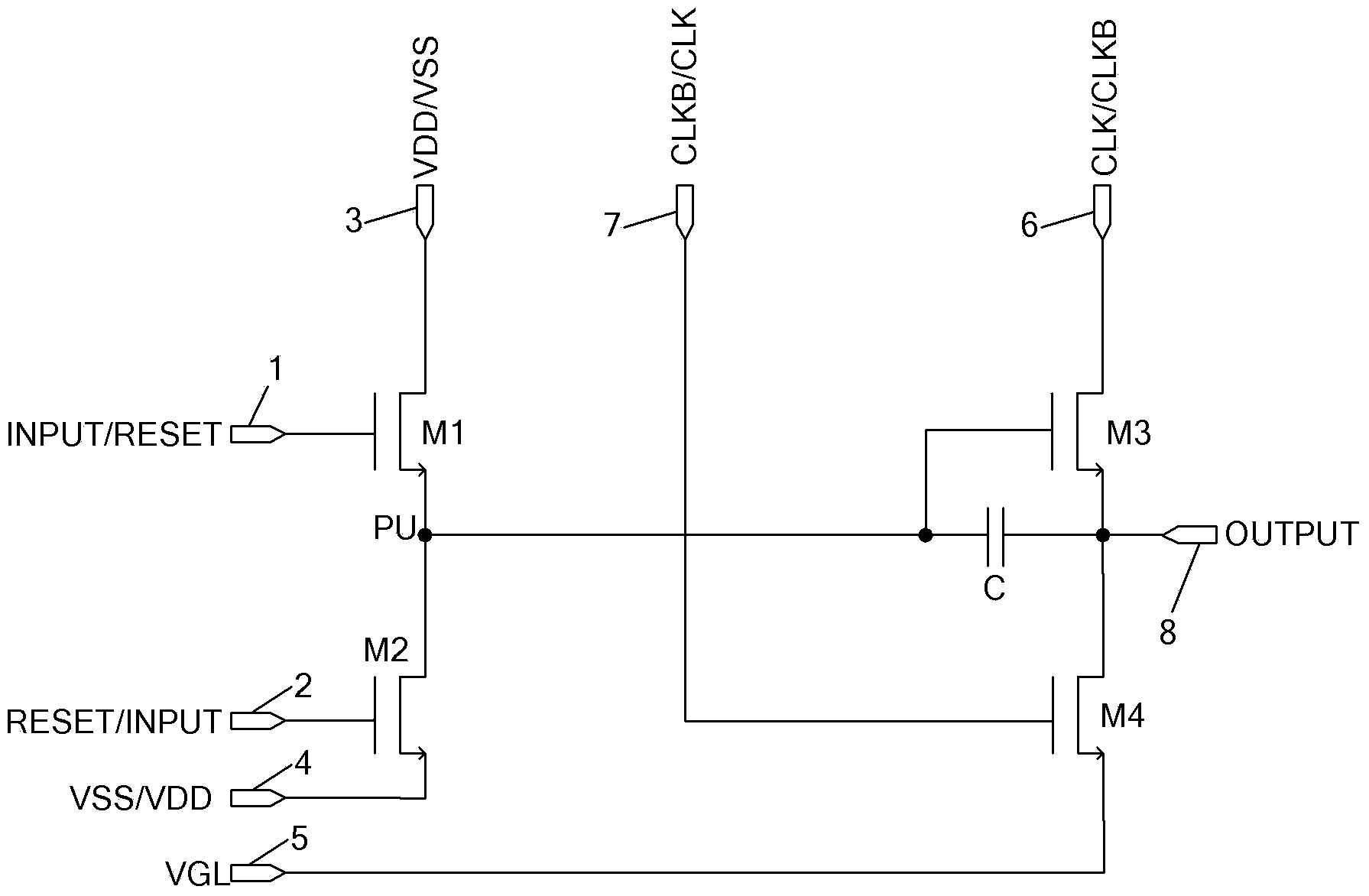

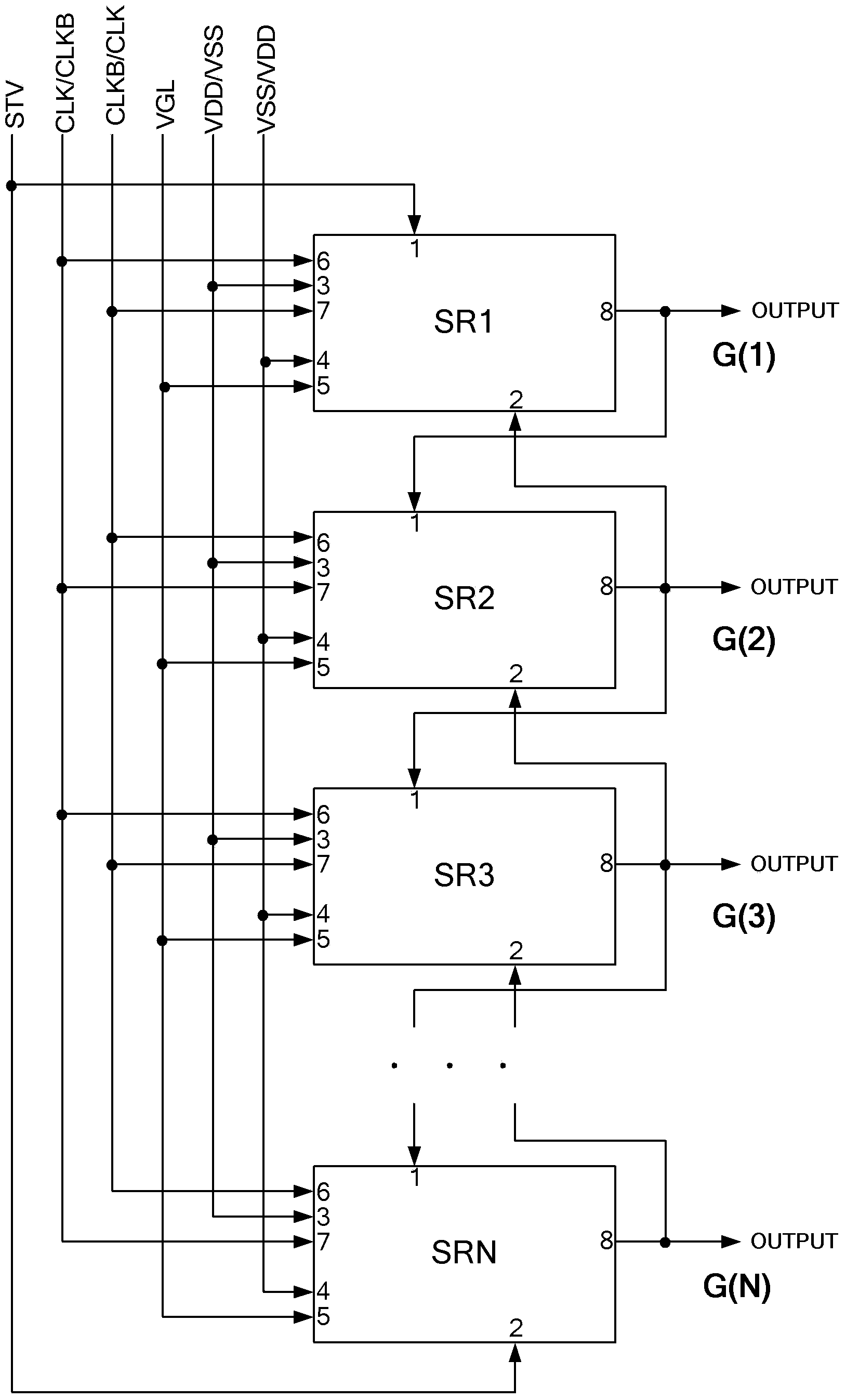

[0044] The first embodiment is a basic implementation circuit of the shift register unit of the present invention, and a basic cascaded circuit constituting the gate drive circuit. figure 2 is a circuit diagram of the shift register unit of this first embodiment. Such as figure 2 As shown, the shift register unit of this embodiment includes at least seven input terminals and one output terminal, and at least four transistors and one capacitor.

[0045] The seven input terminals are the first input terminal 1 , the second input terminal 2 , the third input terminal 3 , the fourth input terminal 4 , the constant low level terminal 5 , the first clock terminal 6 and the second clock terminal 7 . One output is the output 8 . The four transistors are first to fourth transistors M1 to M4. One capacitor is capacitor C.

[0046] The gate of the first transistor M1 is connected to the first input terminal 1, and the source is connected to the third input terminal 3; the gate of t...

no. 2 example

[0069] The second embodiment is an improvement on the basis of the first embodiment. The cascading manner of the gate driving circuits of this embodiment is the same as that of the first embodiment, the difference is the structure of each shift register unit. Figure 5 The circuit configuration of the shift register unit of this embodiment is shown. Such as Figure 5 As shown, compared with the first embodiment, the shift register unit of this embodiment further includes a fifth transistor M5. The source and gate of the fifth transistor M5 are connected, and the source is connected to the second clock terminal 7 , and the drain is connected to the gate of the fourth transistor M4 .

[0070] The function of the fifth transistor M5 is: after the reset period, when the clock signal connected to the second clock terminal 7 is at a low level, the gate of the fourth transistor M4 and the second clock terminal 7 are not conducted to maintain relatively low voltage. High potential,...

no. 3 example

[0072] The third embodiment is also an improvement on the mobile register unit based on the first embodiment. Likewise, the cascading manner of the gate drive circuits of this embodiment is the same as that of the first embodiment, except for the structure of each shift register unit. Image 6 The circuit configuration of the shift register unit of the third embodiment is shown. Such as Image 6 As shown, compared with the first embodiment, the shift register unit of the third embodiment may further include a sixth transistor M6, the source of the sixth transistor M6 is connected to the gate of the fourth transistor M4, and the sixth transistor M6 The drain of M6 is connected to the constant low level terminal 5 . Here, the connection node of the gate of the fourth transistor M4 is referred to as a pull-down node PD.

[0073] In this way, during the pre-charging period and the scan period of the current stage, when the pull-up node PU is at a high voltage, the sixth transis...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More