Semiconductor device with MIM capacitor and formation method thereof

A semiconductor and capacitor technology, applied in the field of semiconductor devices with MIM capacitors and their formation, can solve problems to be improved, and achieve the effect of reducing resistance and improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

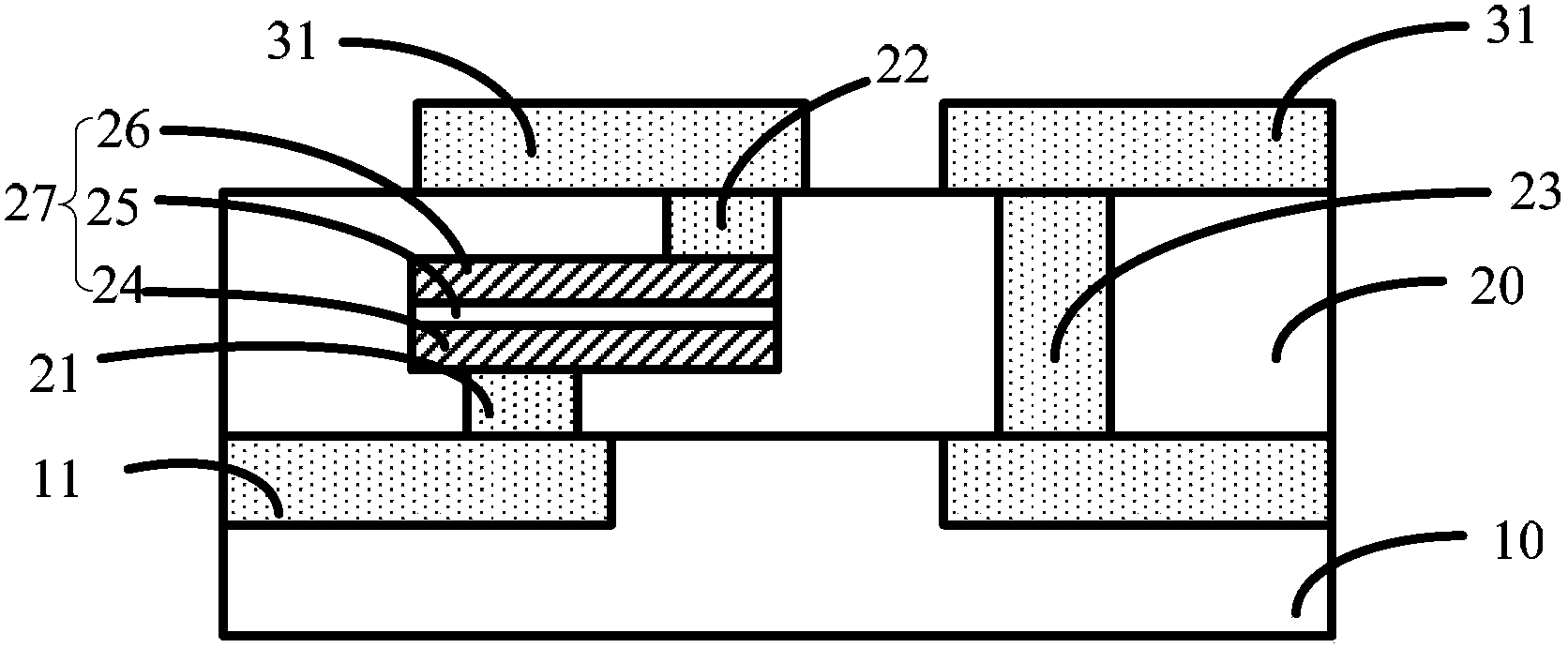

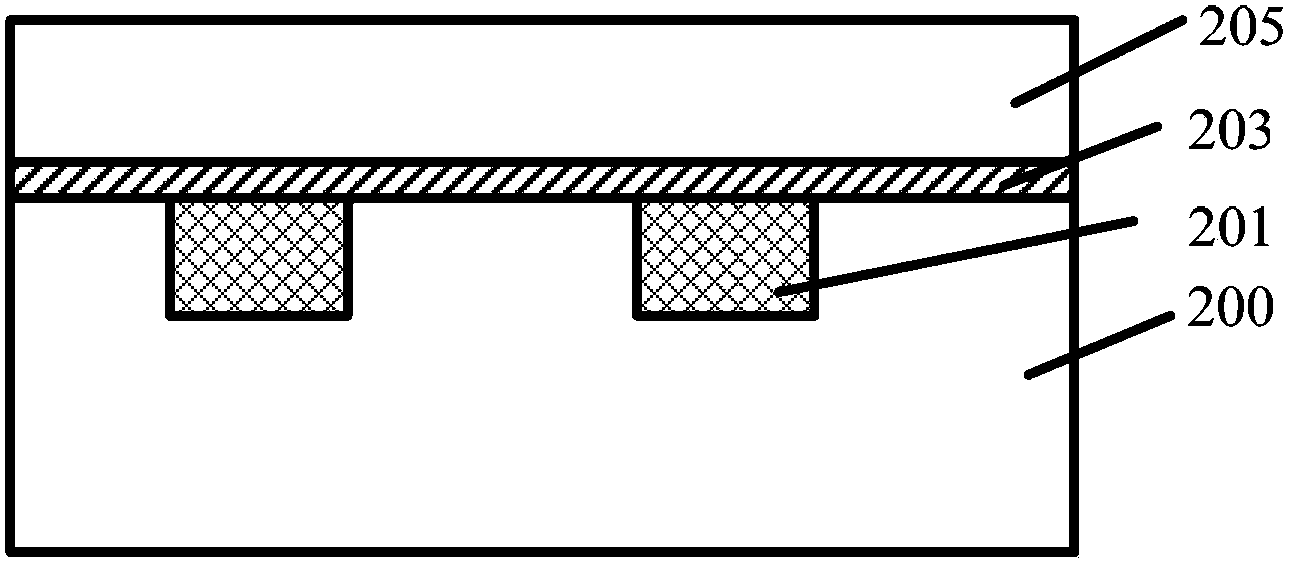

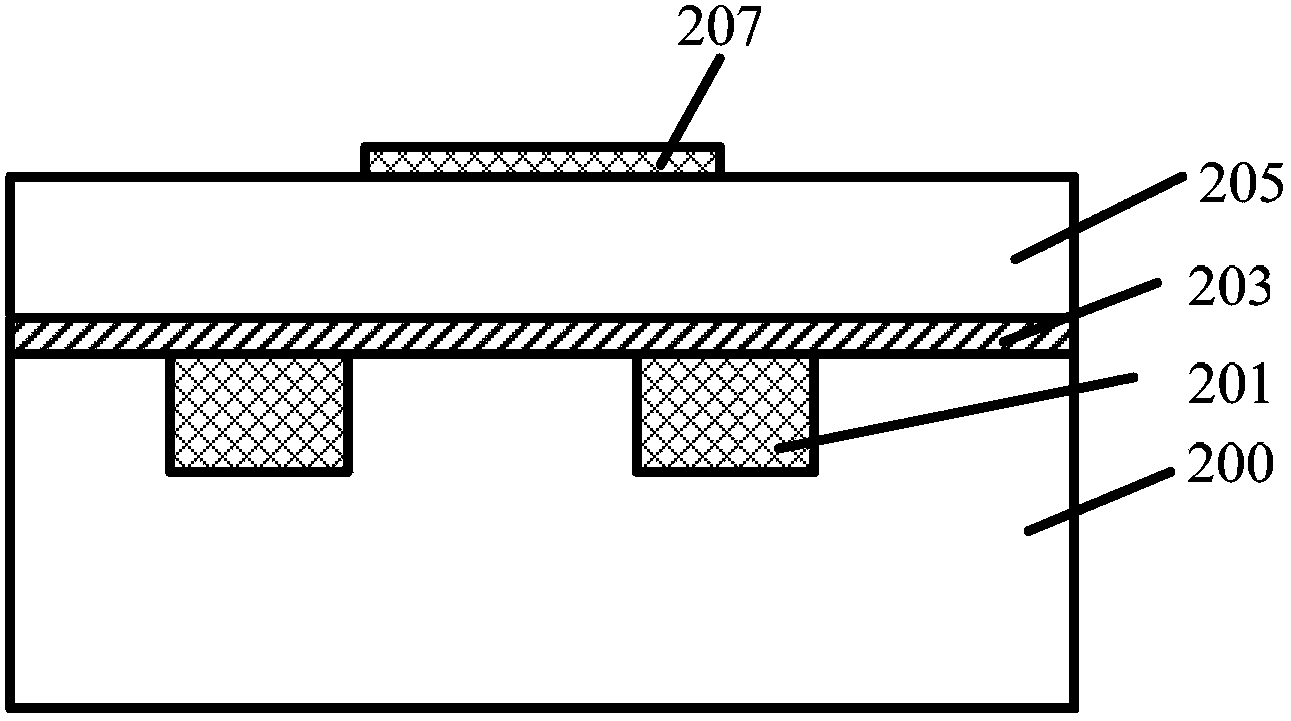

[0043] Specifically, please refer to Figure 2-Figure 9 , Figure 2-Figure 9 A schematic cross-sectional structure showing the formation process of the semiconductor device with MIM capacitor according to the first embodiment of the present invention.

[0044] Please refer to figure 2 , providing a substrate 200 and a first interlayer dielectric layer 205 covering the substrate 200 .

[0045] The base 200 is used to provide a platform for subsequent processes, and the base 200 includes a semiconductor substrate (not shown) and an initial interlayer dielectric layer (not shown) on the surface of the semiconductor substrate. Wherein, the material of the semiconductor substrate is single crystal silicon, single crystal germanium, III-V compound or silicon-on-insulator, etc., and the material of the initial interlayer dielectric layer is low-K material, ultra-low-K material or oxide Wait.

[0046] In the embodiment of the present invention, it also includes: forming an intercon...

no. 2 example

[0097] Different from the first embodiment of the present invention, only one conductive plug is electrically connected to the interconnection metal layer 301 in the second embodiment.

[0098] Please refer to Figure 10 , Figure 10 A schematic cross-sectional structure showing the formation process of the semiconductor device with MIM capacitor according to the second embodiment of the present invention.

[0099] providing a substrate 300 and a first interlayer dielectric layer 305 covering the substrate 300;

[0100] forming an interconnect metal layer 301 within the substrate;

[0101] forming a MIM capacitor located on the surface of the first interlayer dielectric layer 305, the MIM capacitor comprising a bottom electrode layer 307 and a top electrode layer 311a which are isolated from each other and crossed laterally;

[0102] forming a second interlayer dielectric layer 315 covering the surface of the MIM capacitor and the first interlayer dielectric layer 305;

[...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More