P-type fin field effect transistor and method of forming the same

A fin-type field effect and transistor technology, which is applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of small stress of the silicon germanium layer 104, easy contact of the silicon germanium layer 104, leakage current, etc., to prevent The effect of the dislocation effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

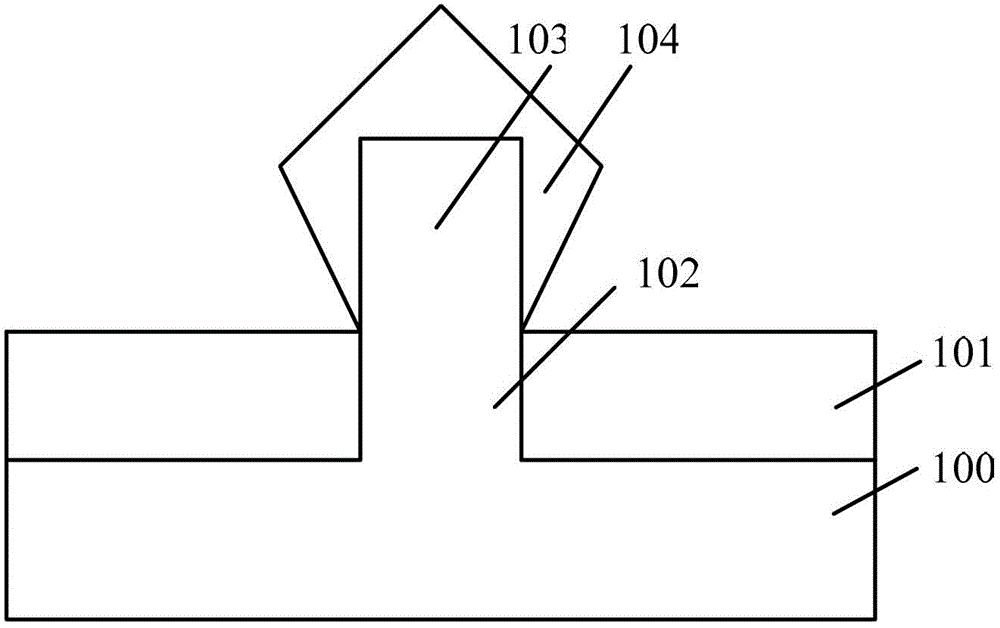

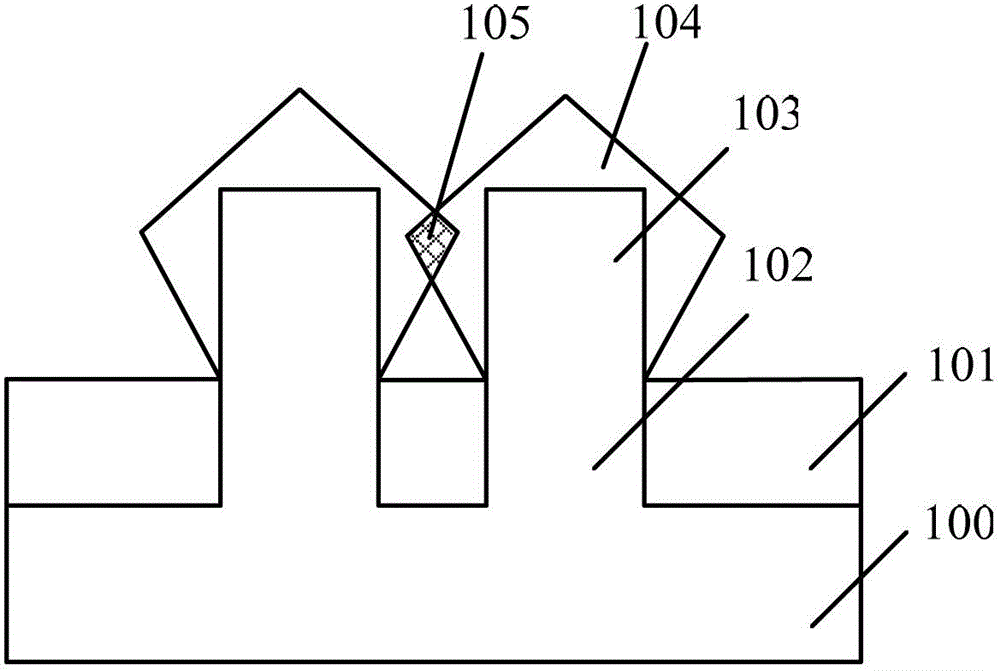

[0035] It can be known from the background art that when a fin-type field effect transistor with embedded source and drain regions is formed in the prior art, the embedded source / drain regions of two adjacent fin-type field effect transistors are easy to contact, and leakage current is generated.

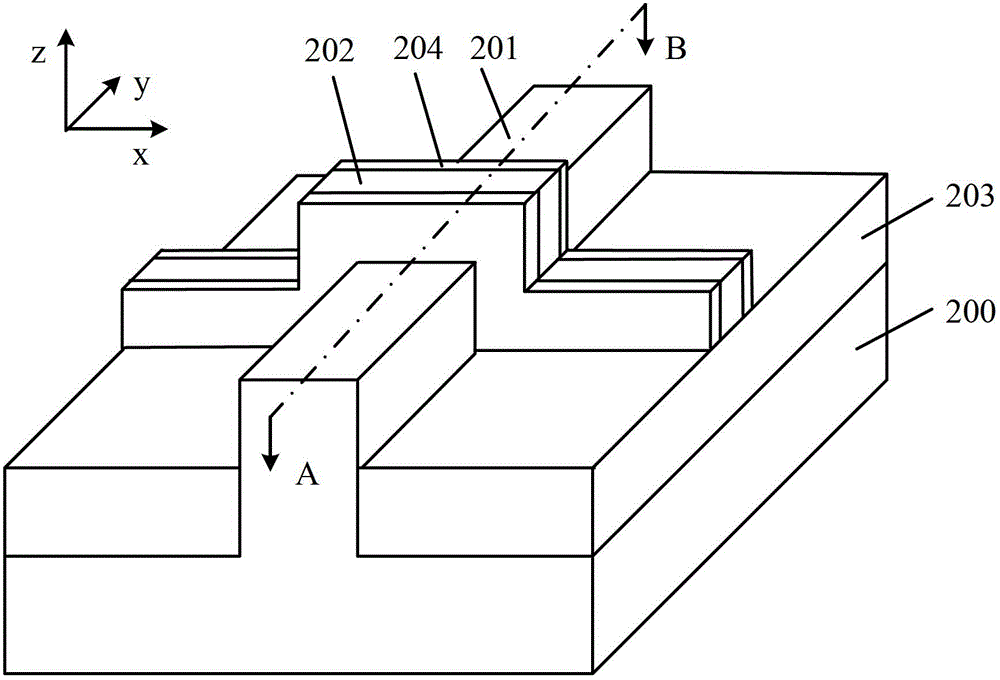

[0036] The inventor of the present invention studied the formation process of forming fin-type field effect transistors in the prior art and found that the easy contact between the silicon germanium layers of two adjacent fin-type field effect transistors in the prior art is due to the formation of the epitaxial layer When the semiconductor material has different growth rates on different crystal planes, the formed silicon germanium layer has irregular shapes, angular and protruding tips. As the feature size continues to decrease, the adjacent fin field effect transistors The silicon germanium layer formed on the source / drain regions is prone to bridging.

[0037] The inventor further re...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More