FPGA (field programmable gate array)-based UKF (unscented Kalman filter) algorithm and filtering on brain dynamics model by FPGA-based UKF algorithm

A dynamic model and algorithm technology, applied in the intersection of digital integrated circuits and neural dynamics, can solve problems such as poor real-time performance, single dot matrix display, and difficulty in hardware implementation of unscented Kalman filtering. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] The specific embodiments of the present invention will be further described in detail below with reference to the accompanying drawings.

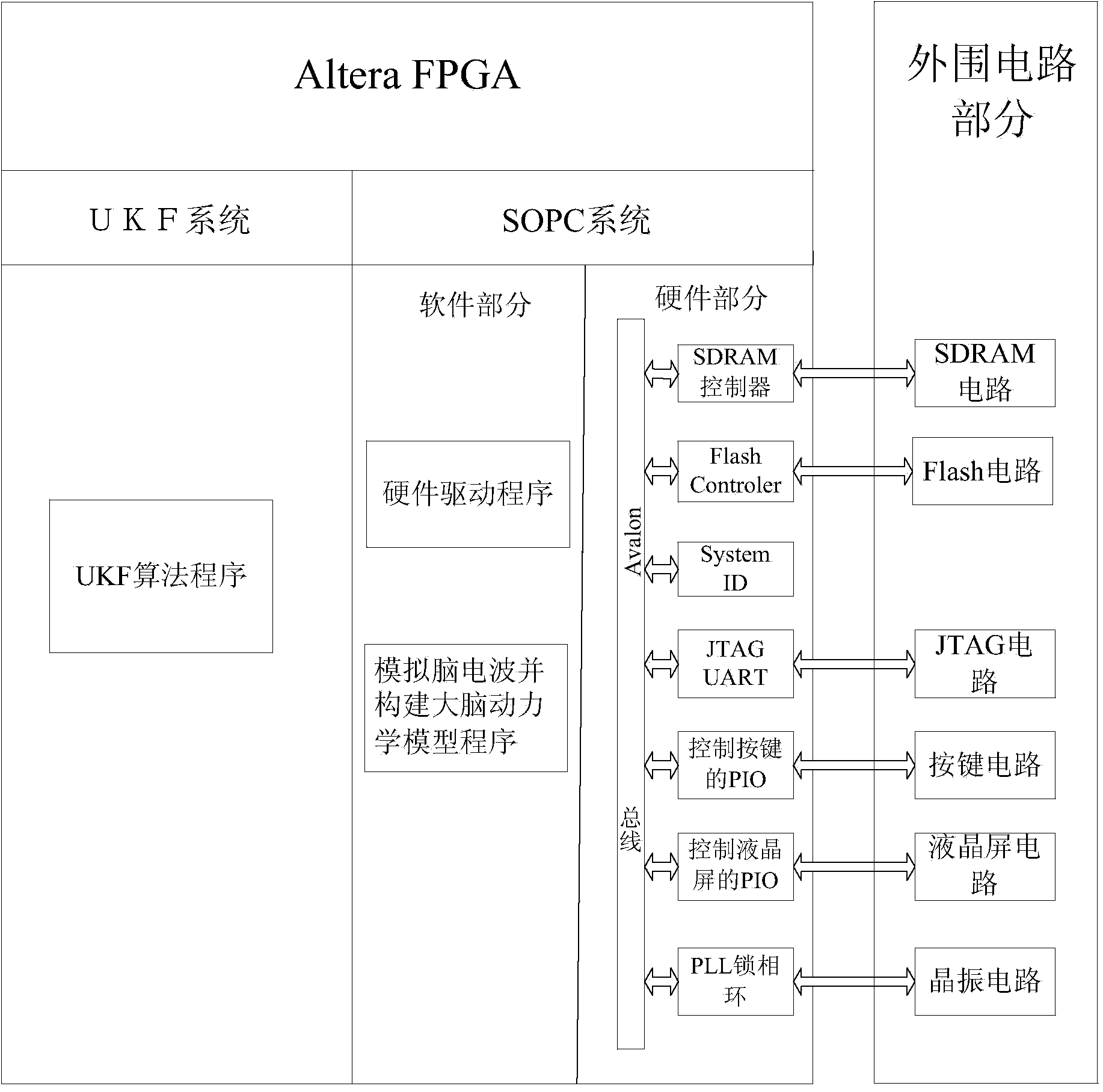

[0044] figure 1 It is the overall structure diagram of the present invention, wherein the FPGA is produced by Altera Company, and the model is EP4CE15F17C8. Two systems are embedded in the FPGA, namely the UKF system written in the hardware description language Verilog HDL and the SOPC system with NIOS II as the core. The filtering of the constructed brain dynamics model, and simultaneously outputting the waveform before filtering and the waveform after filtering to the TFT liquid crystal screen, the specific implementation manner and process are as follows.

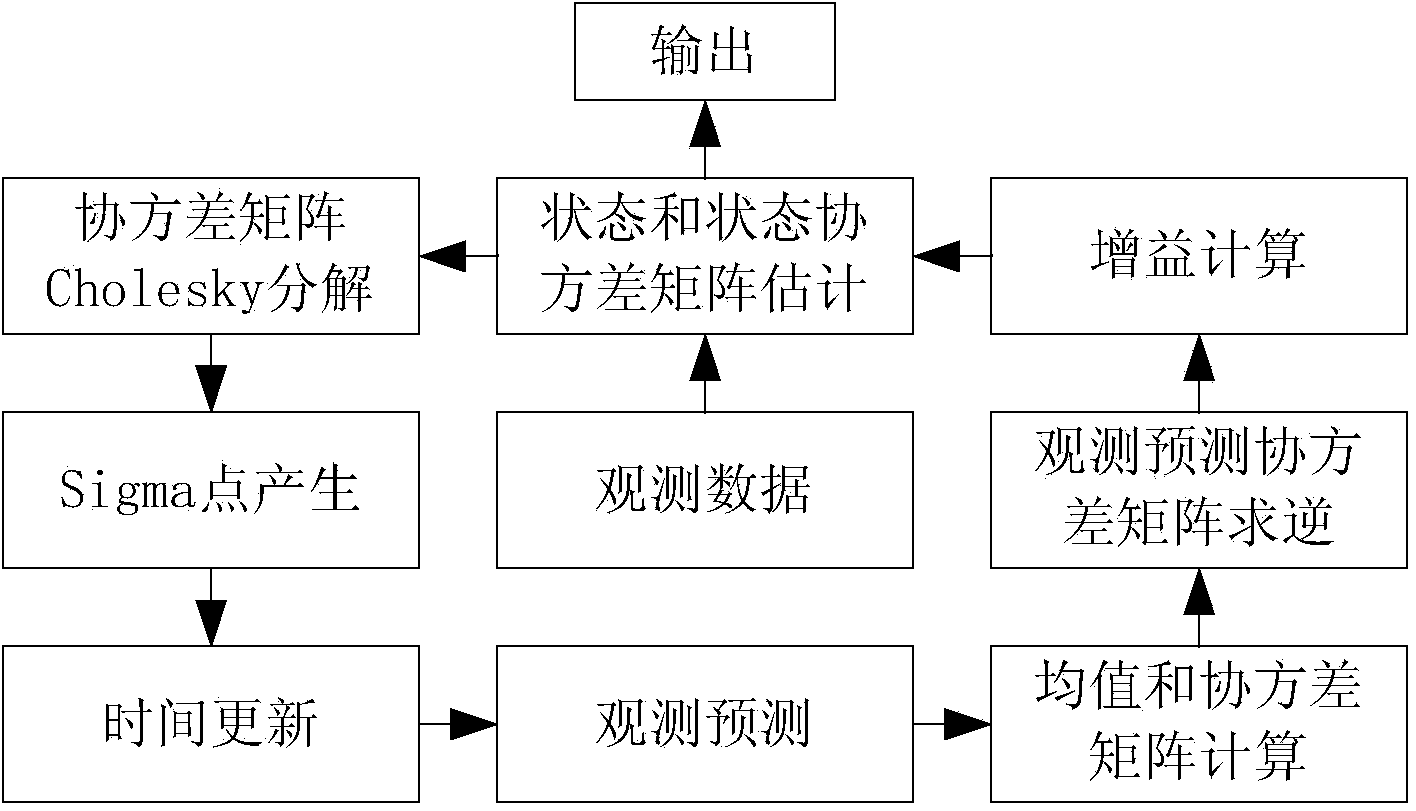

[0045] The UKF algorithm is implemented in the UKF system. The flow chart of the UKF algorithm is as follows figure 2 The modules involved include: covariance matrix Cholesky decomposition module, Sigma point generation module, time update module, observation prediction modu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More