Conductive plug and TSV forming method

A technology of conductive plugs and semiconductors, which is applied in the manufacture of circuits, electrical components, semiconductors/solid-state devices, etc., and can solve problems affecting the stability of TSV conduction, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

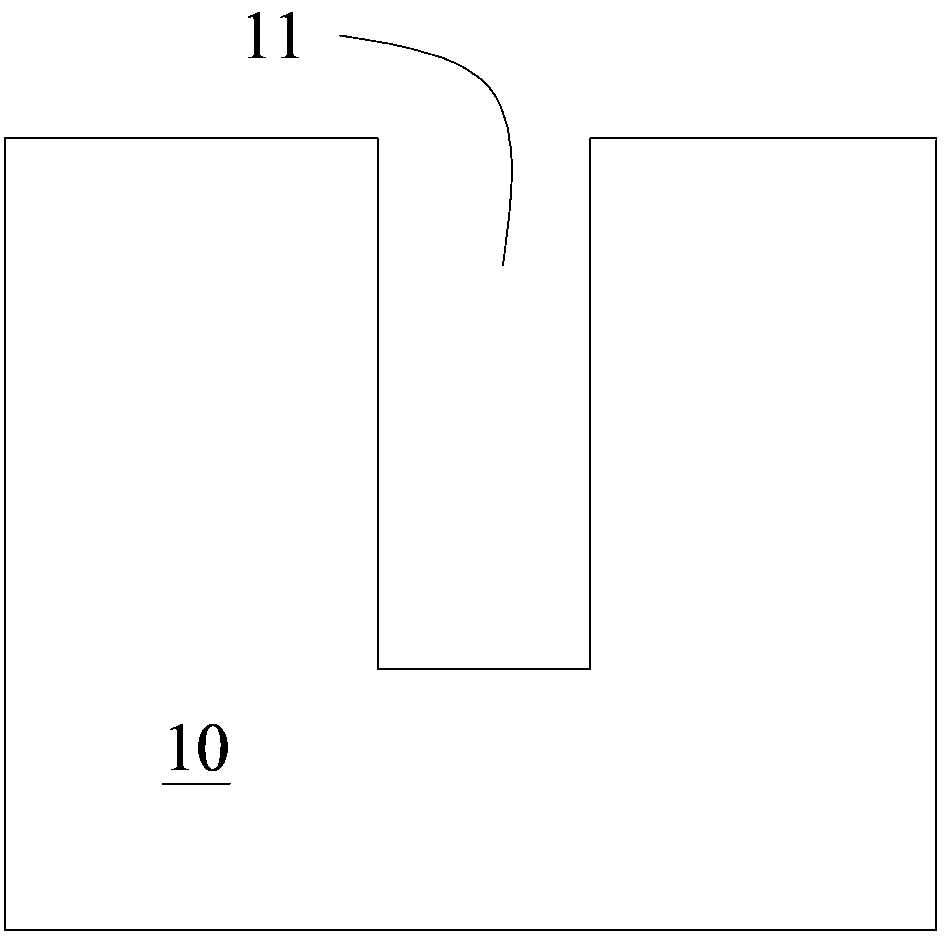

[0049] refer to figure 2 As shown, a semiconductor substrate 100 is provided, and the semiconductor substrate 100 includes an upper surface 200 and a lower surface 300 . The material of the semiconductor substrate 100 can be silicon, germanium, gallium arsenide or silicon germanium compound. Existing semiconductor substrates can all be used as the semiconductor substrate 100 of the present invention, and will not be listed here. In this embodiment, the semiconductor substrate 100 is preferably made of silicon.

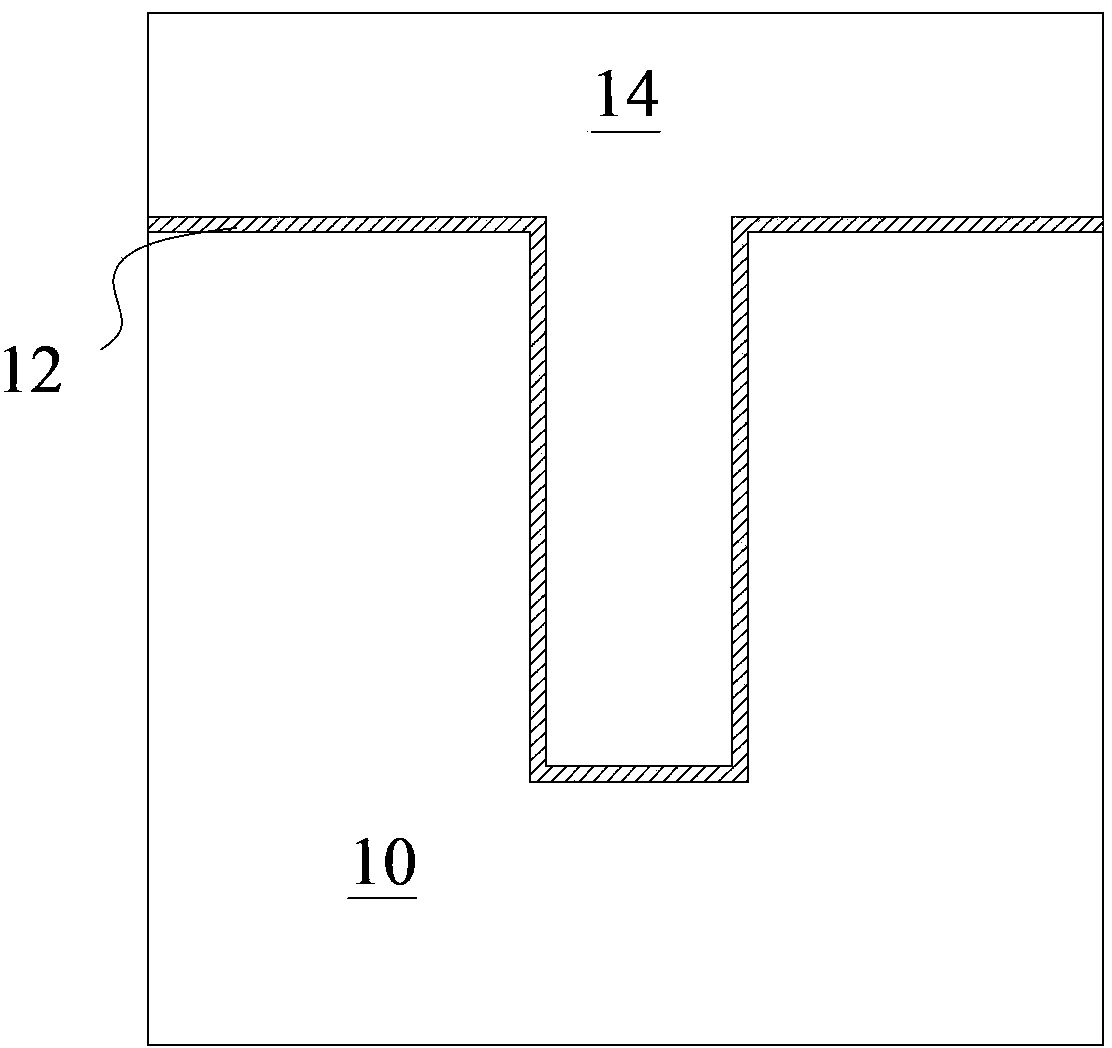

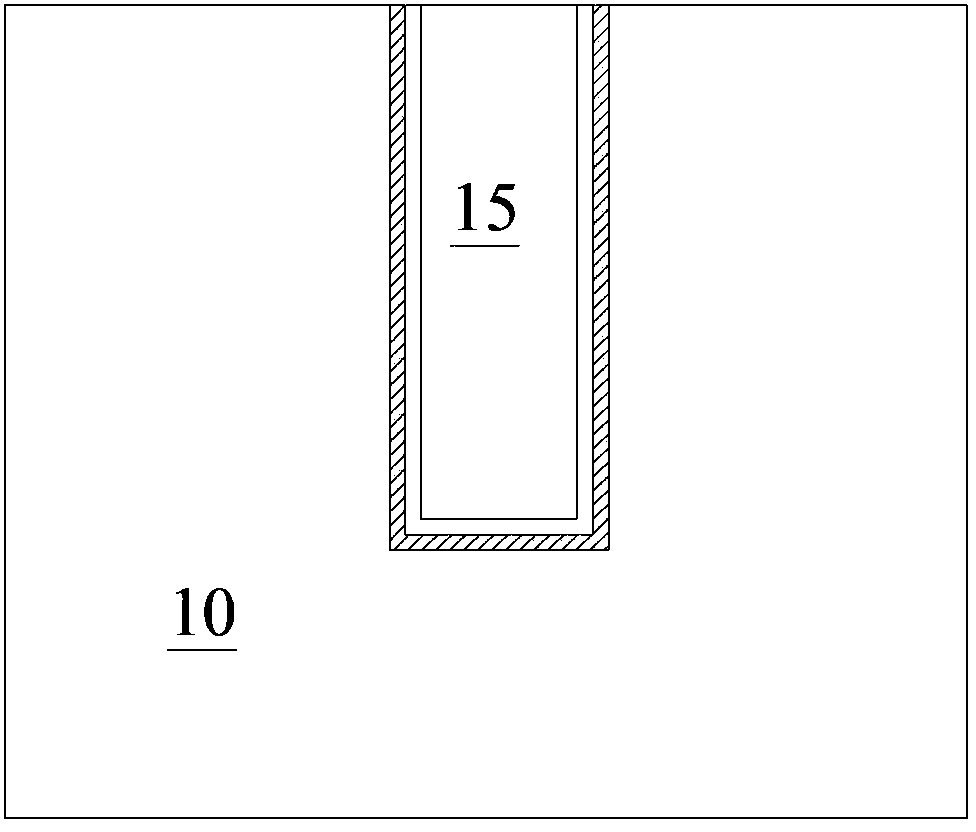

[0050] refer to image 3 As shown, the semiconductor substrate 100 is etched to form a blind hole 110 in the semiconductor substrate 100 . The specific process includes: coating a hard mask layer 101 on the upper surface 200 of the semiconductor substrate 100, and patterning the hard mask layer 101 by a process such as photolithography, and forming in the hard mask layer 101 Opening (marked in figure). Afterwards, using the patterned hard mask layer 101 as a mask...

Embodiment 2

[0065] The method for forming the conductive plug provided in this embodiment is substantially the same as the technical solution of the method for forming the conductive plug provided in Embodiment 1, the only difference being that before the annealing process, the CMP process is used to remove the covering on the semiconductor substrate 100. The entire thickness of the upper surface of the metal layer 104 further ensures that the stress generated in the semiconductor substrate 100 , the metal layer 104 , the metal shielding layer 103 and the insulating layer 102 during the annealing process is fully released.

[0066] After the conductive plug 106 is formed as in Embodiment 1 and Embodiment 2, refer to Figure 8 As shown, the lower surface 300 of the semiconductor substrate 100 is polished by a process such as CMP, so that the conductive plug 106 is connected to the blind hole 110 to form a TSV in the semiconductor substrate 100 . And in the subsequent packaging process, the...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More