Double-graphene-layer tunneling field effect transistor and manufacturing method thereof

A double-layer graphene and tunneling field effect technology, applied in the field of nanoelectronics, can solve the problems that limit the wide application of TFET, low tunneling probability, etc., and achieve the effect of small off-state current and simple preparation process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The present invention will be further described below by example. It should be noted that the purpose of the disclosed embodiments is to help further understand the present invention, but those skilled in the art can understand that various replacements and modifications are possible without departing from the spirit and scope of the present invention and the appended claims of. Therefore, the present invention should not be limited to the content disclosed in the embodiments, and the protection scope of the present invention is subject to the scope defined in the claims.

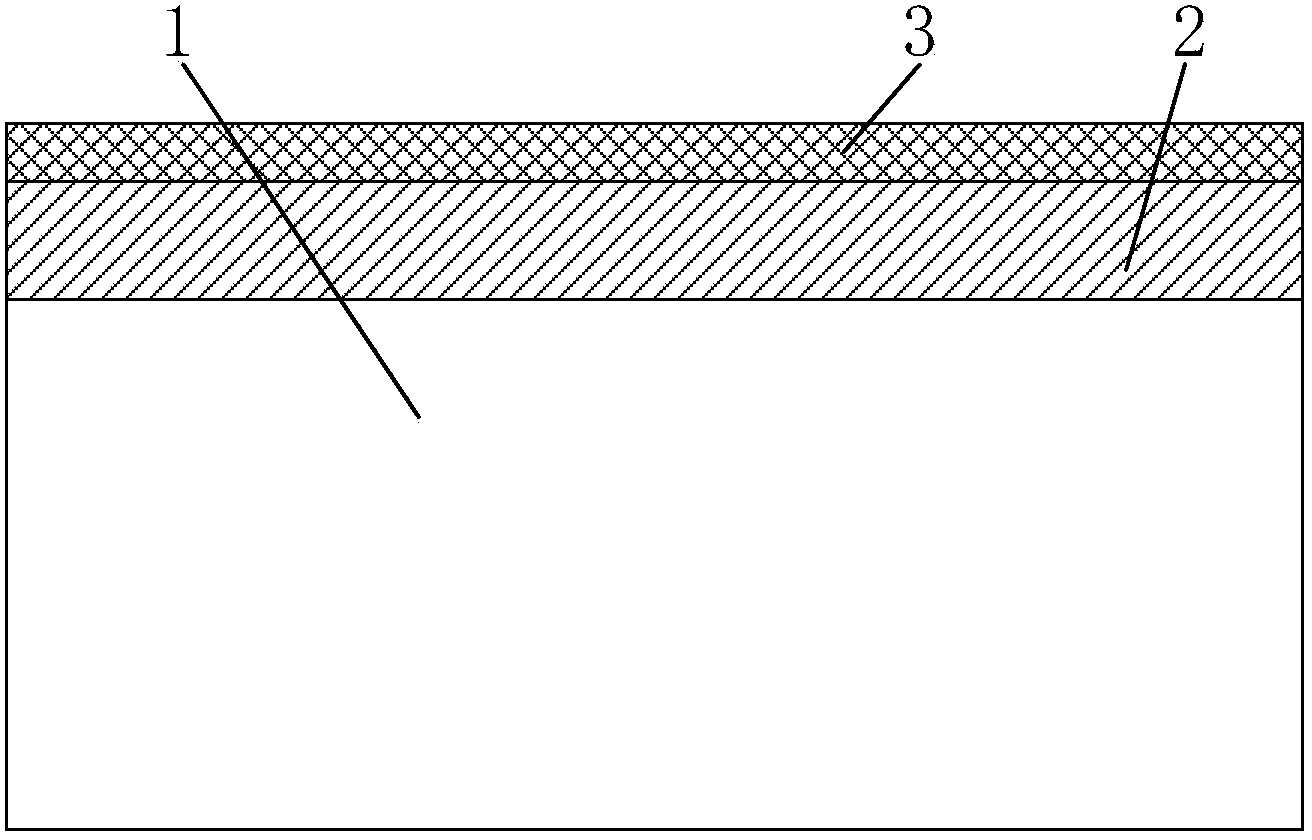

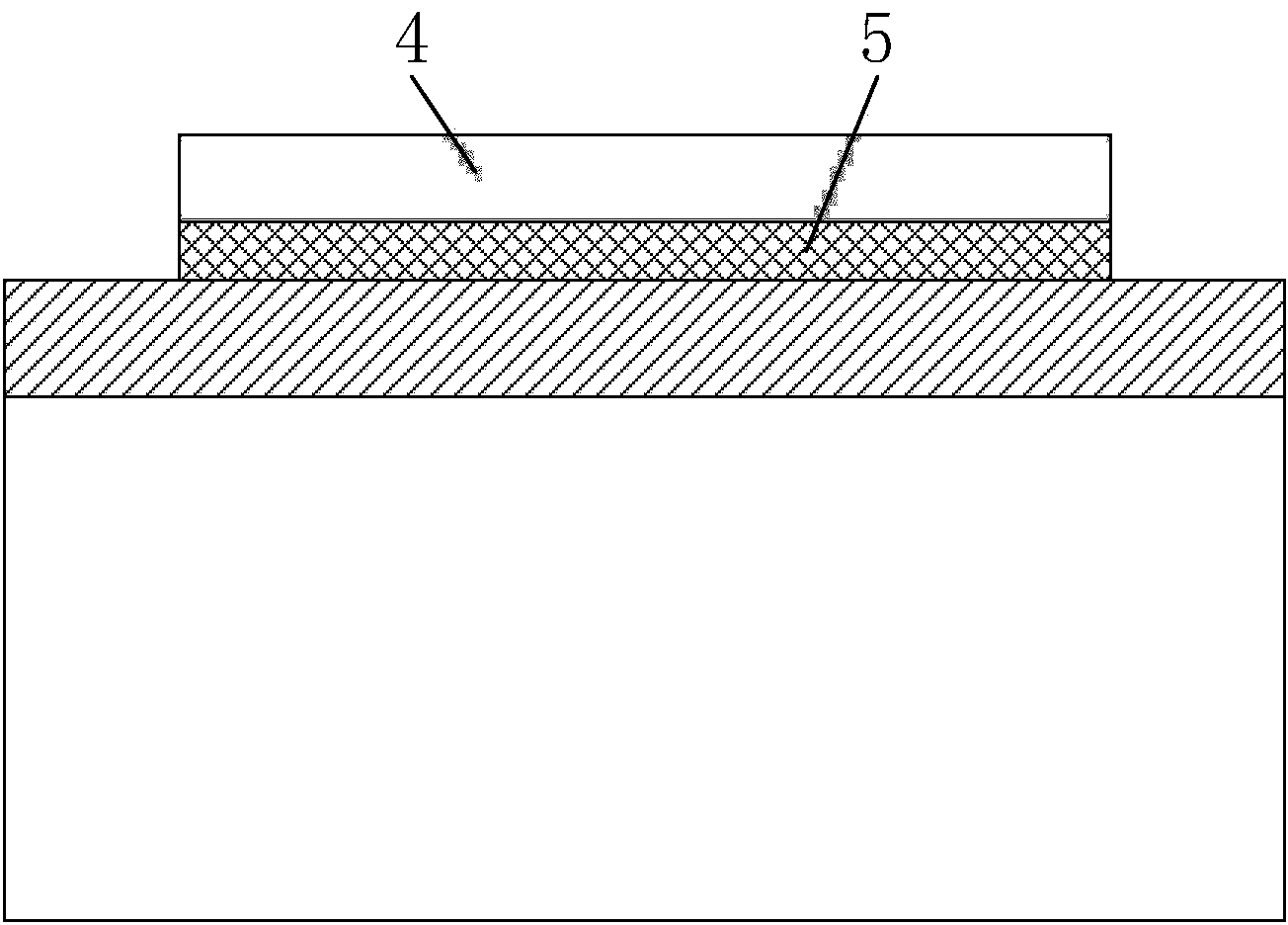

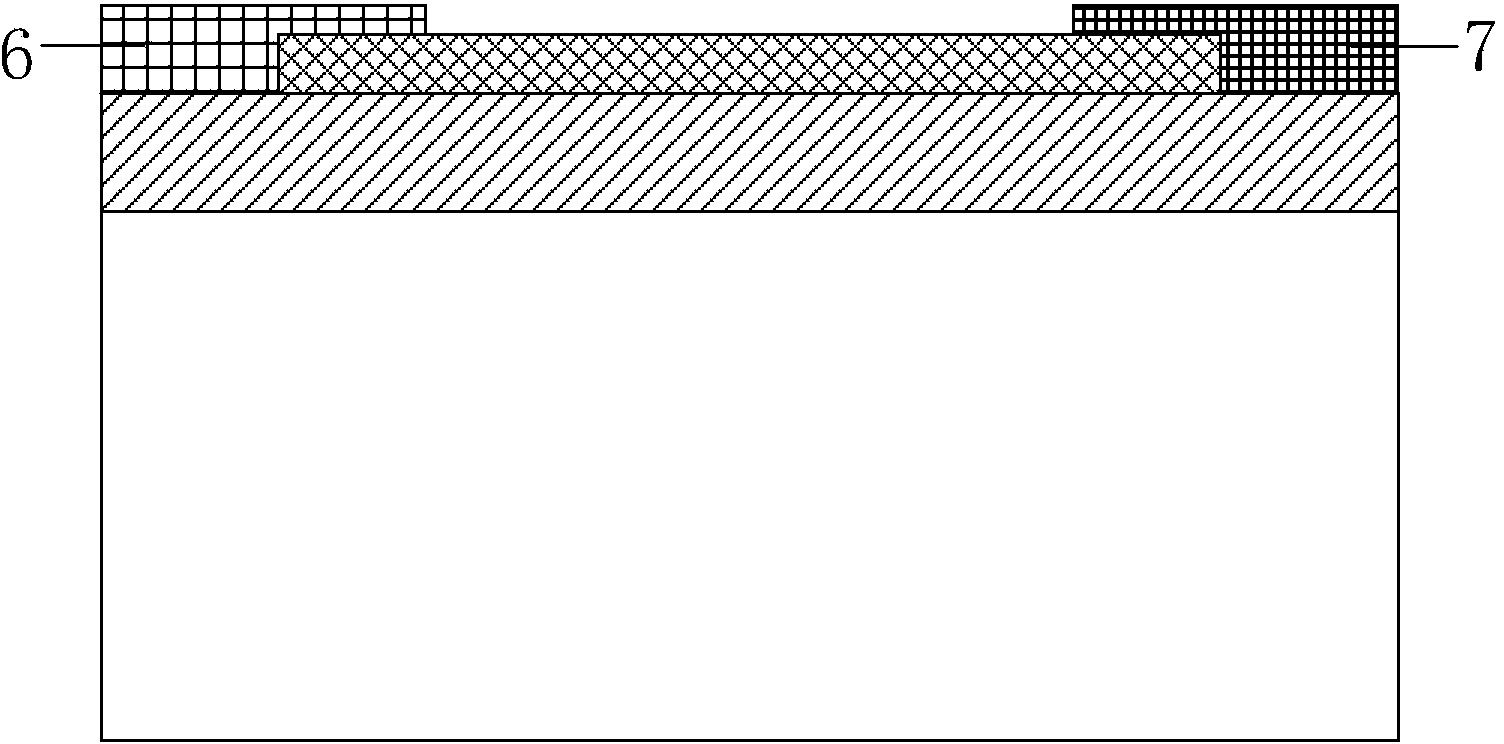

[0039] A specific example of the preparation method of the present invention includes Figure 1 to Figure 5 Process steps shown:

[0040] 1) A low-resistance silicon wafer with (100) crystal orientation is used as the bottom gate electrode 1, and a layer of bottom gate dielectric layer 2 is thermally oxidized on its surface, and the bottom gate dielectric layer is SiO 2 , with a thickness of 90nm;...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More