Single Event Upset and Single Event Transient Immunity Latch

A single-event transient and anti-single-event technology, applied in the direction of pulse technology, electrical components, logic circuits, etc., can solve the problems of unable to shield combinational logic, unsuitable for high-reliability integrated circuit systems, soft errors, etc., and achieve power consumption And the effects of small area overhead, high reliability, and improved radiation resistance performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

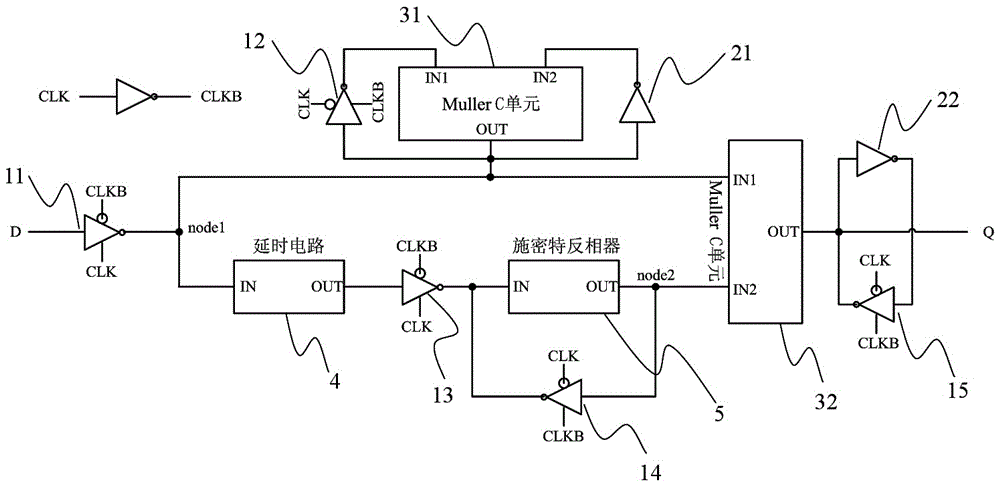

[0027] In order to make the purpose, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings. The specific implementation cases described here are only used to illustrate the present invention, and are not intended to limit the present invention. figure 2 Shown is the schematic diagram of the latch circuit of the present invention, and its specific structure is as follows:

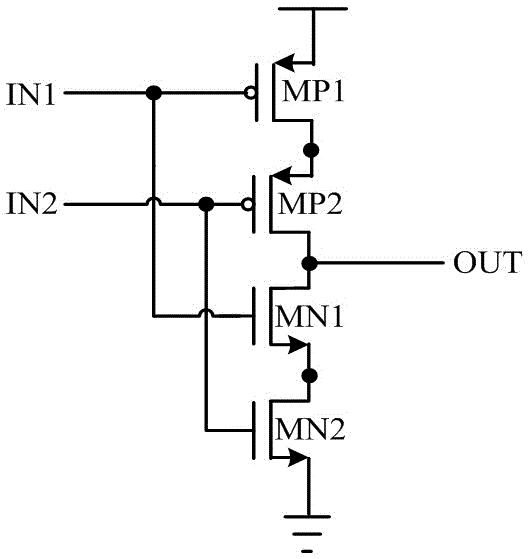

[0028] A latch resistant to single-event upsets and single-event transient pulses, comprising five clocked inverters, two conventional inverters, two Muller C cell circuits, a delay circuit4, and a Schmitt Inverter 5; the five clocked inverters are successively the first clocked inverter 11, the second clocked inverter 12, the third clocked inverter 13, and the fourth clocked inverter 14 and the fifth clocked inverter 15; two conventional inverters are the first conventional inverter ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More