High-integration-level and high-mobility-ratio source, drain and gate auxiliary control type junction-free transistor

A junction-free transistor and high-mobility technology, which is applied in semiconductor devices, electrical components, circuits, etc., can solve problems affecting device turn-on characteristics, device mobility decline, device reliability, etc., to overcome short-channel effects, Effects of low source-drain resistance and increased effective channel length

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

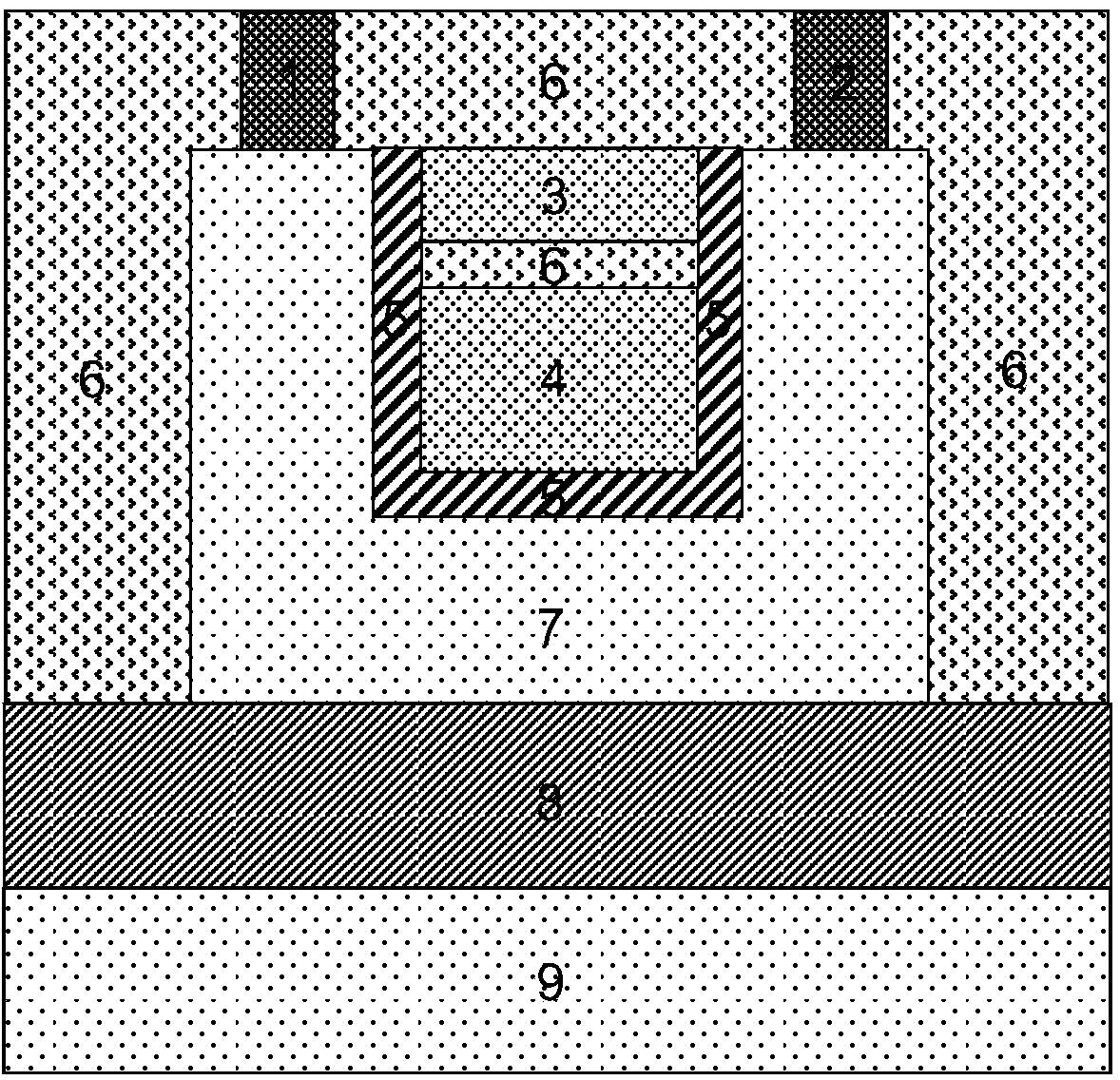

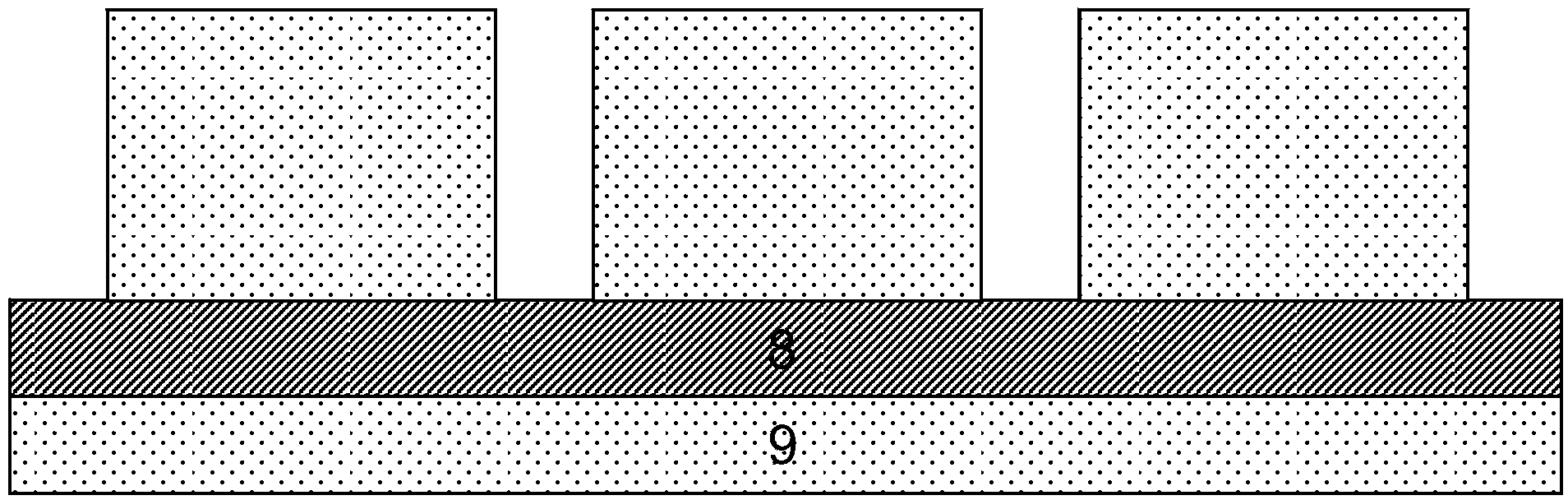

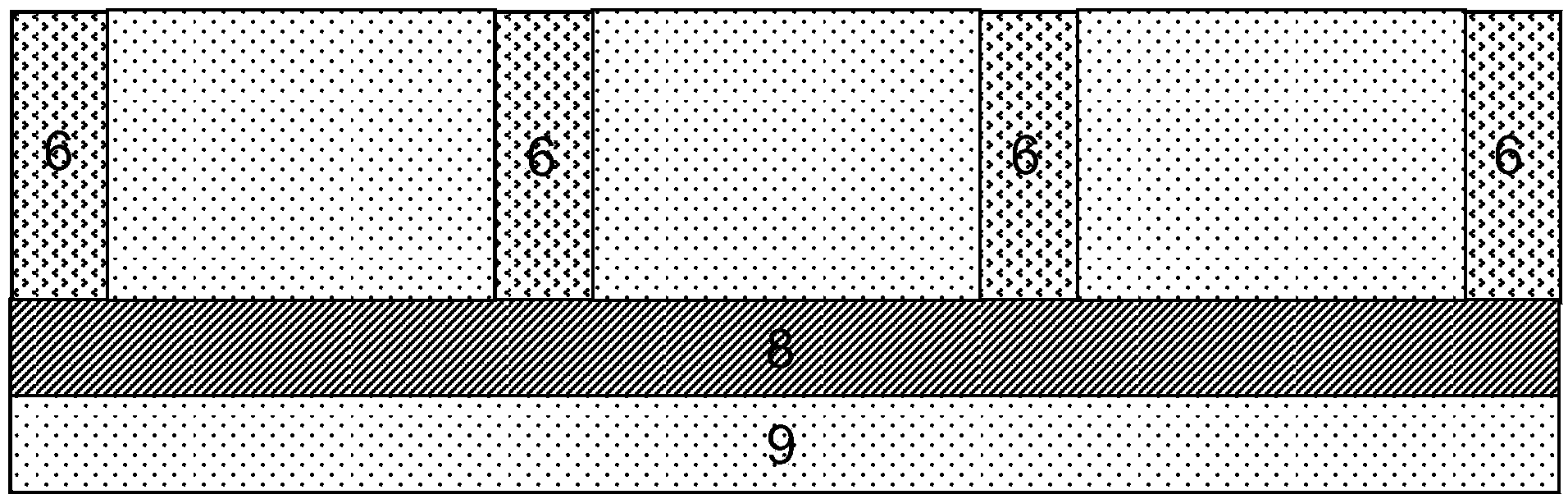

[0027] Below in conjunction with accompanying drawing, the present invention will be further described:

[0028] The high-integration, high-mobility source-drain-gate assisted junction-free transistor of the present invention, through the joint action of the source-drain control gate electrode 3 and the gate electrode 4, which are independently controlled electrodes, can be used under the condition of low doping concentration. A junction-free transistor with high mobility and low source-drain resistance is realized. Taking the N-type as an example, when the device is working, the source-drain control gate electrode 3 always maintains a constant high potential, so that the left and right sides of the source-drain control gate electrode 3 correspond to the single crystals under the source electrode 1 and the drain electrode 2 respectively. The left and right ends of the silicon groove 7 form electron accumulation, and the accumulated electrons enhance the conductivity of the lef...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More