Silicon/germanium-silicon vertical nodded type field effect transistor

A field-effect transistor, junction technology, used in transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve problems such as size limits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

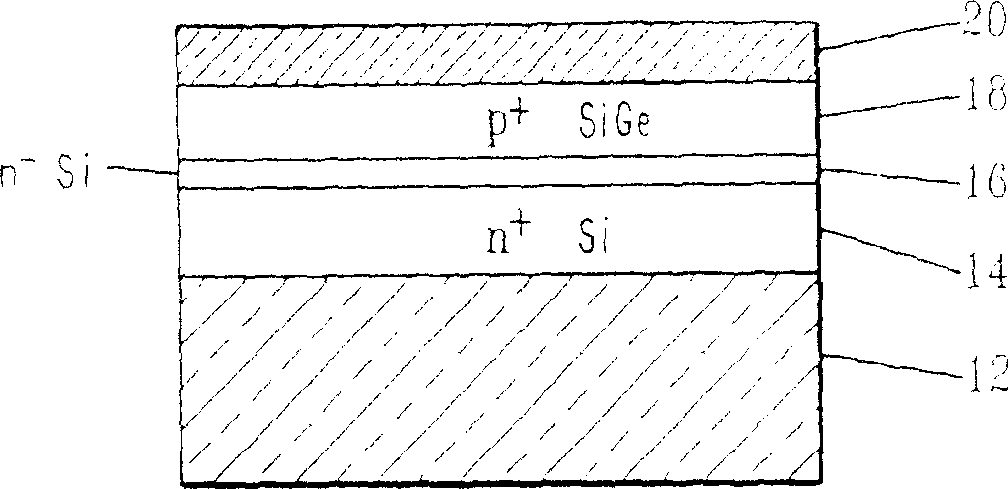

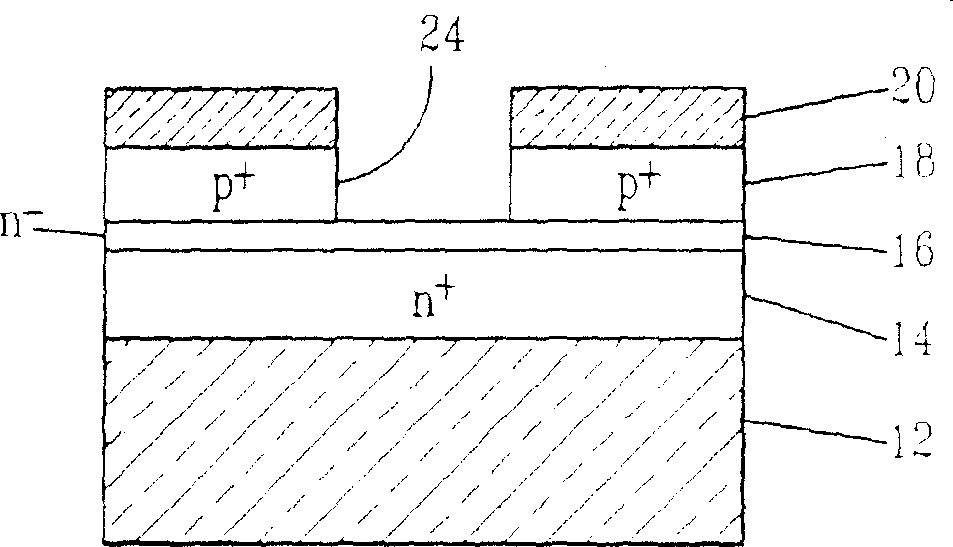

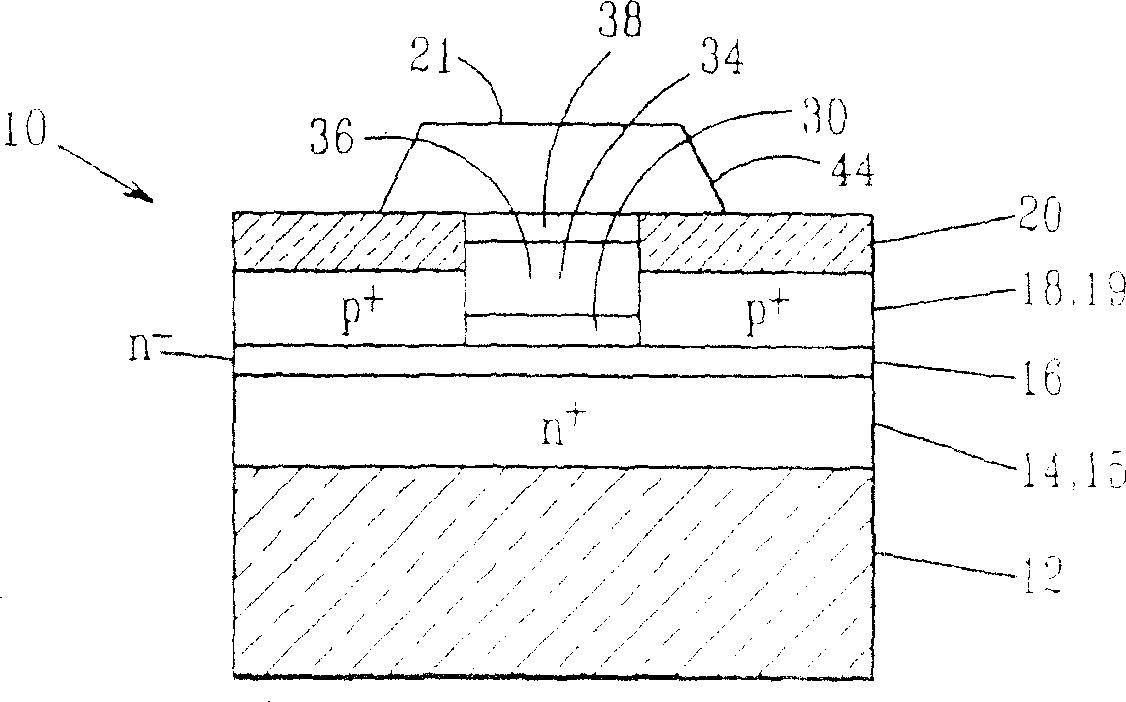

[0026] Referring now to the accompanying drawings, in particular Figure 1-3 , shows the steps of fabricating a vertical junction field effect transistor (JFET) 10 . The starting substrate 12 may be an insulator such as silicon dioxide, or the substrate 12 may be a semiconductor such as monocrystalline silicon, silicon germanium, or silicon-on-insulator. On the substrate 12 may be formed a p-doped semiconductor single crystal layer 14, such as silicon or silicon germanium. The starting substrate 12, if an insulator, and the layer 14 can be formed by isolation by implantation of oxygen (SIMOX), which is well known in the art, or by bonding and etching back an oxide-coated wafer and a semiconductor carrier substrate to Silicon-on-insulator (BESOI) is formed. Layer 14 may be a heavily doped n+ layer to form image 3 Drain electrode 15 of JFET 10 is shown.

[0027] Epitaxial layer 16 is formed on layer 14 , which may be a doped n-layer to reduce the capacitance of gate layer 18...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More