Decimal and integer frequency divider circuit and implementation method thereof

An integer frequency division and frequency divider technology, which is applied in the direction of electrical components and automatic power control, can solve the problems of reducing the phase noise performance of the frequency synthesizer, insufficient phase noise suppression ability, and longer loop locking time, etc., to achieve Improve the operating frequency range, reduce design redundancy, and design flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments.

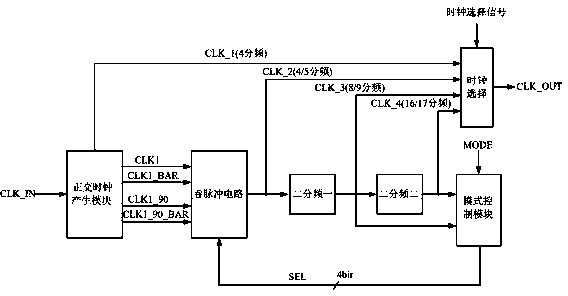

[0023] see figure 1 As shown, a fractional-integer frequency division circuit of the present invention mainly includes a quadrature clock generation module, a pulse swallowing circuit, a frequency divider by two, a mode control module and a clock selection module.

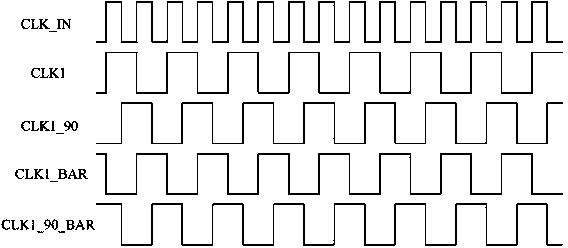

[0024] combine figure 1 As shown, the fractional_integer frequency division circuit first passes the high-frequency clock CLK_IN through the orthogonal clock generation module to generate two pairs of differential signals that are mutually orthogonal, wherein the first pair of differential signals is CLK1 and CLK1_BAR, and the second pair The differential signals are CLK1_90 and CLK1_90_BAR, CLK1 and CLK1_90 have a phase shift of 90 degrees, and the output waveform schematic diagram is as follows figure 2 shown;

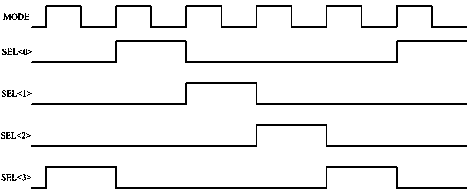

[0025] At the same time, the mode control signal MODE g...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More