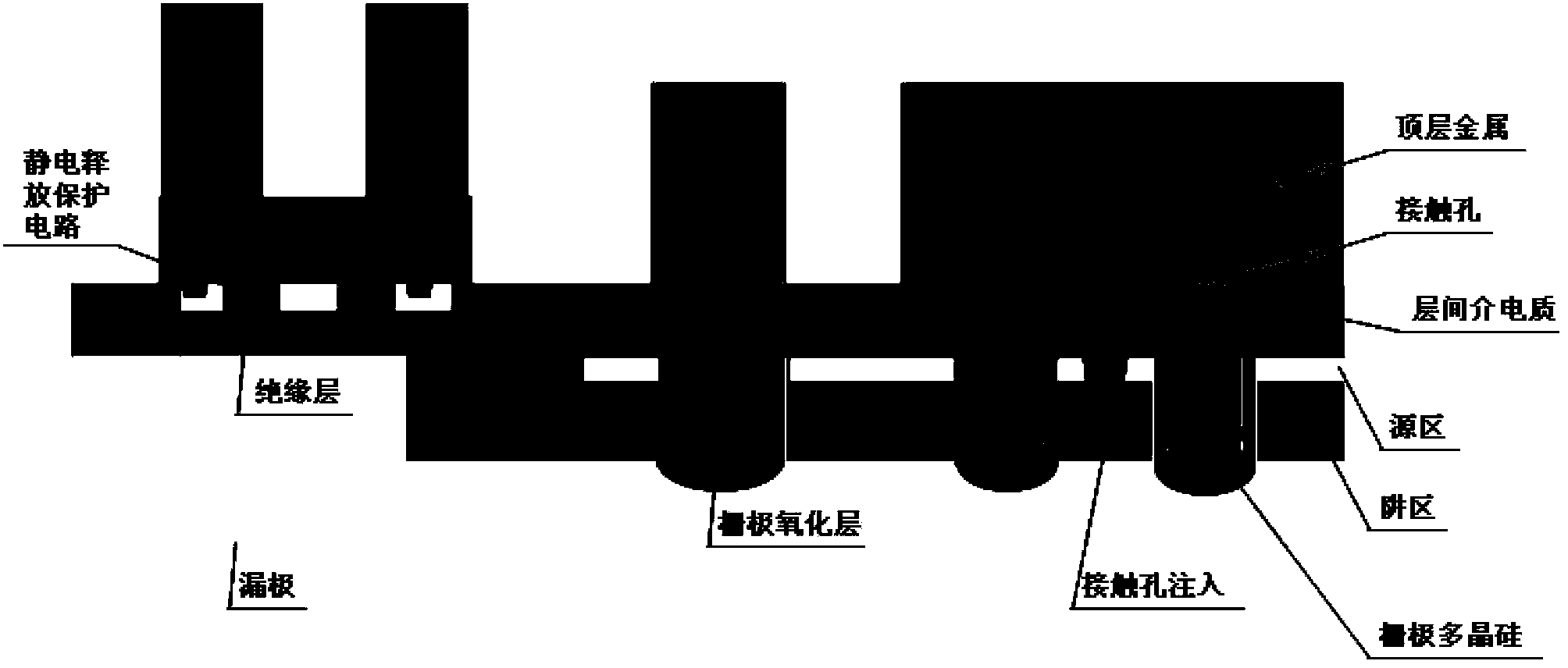

Manufacturing method of groove type MOS (Metal Oxide Semiconductor) transistor with electrostatic discharge protection circuit

A technology for MOS transistors and protection circuits, which is applied in the field of trench MOS transistor manufacturing, can solve problems such as metal etching residues and difficulties in subsequent process planarization, and achieve the goals of improving flatness, reducing residual risks, and shortening the process flow Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] In order to have a more specific understanding of the technical content, characteristics and effects of the present invention, now in conjunction with the illustrated embodiment, the details are as follows:

[0034] The trench power MOS transistor with electrostatic discharge protection circuit of the present invention improves the gate channel and dielectric layer structure on the basis of the original structure, and its specific process realization process is as follows:

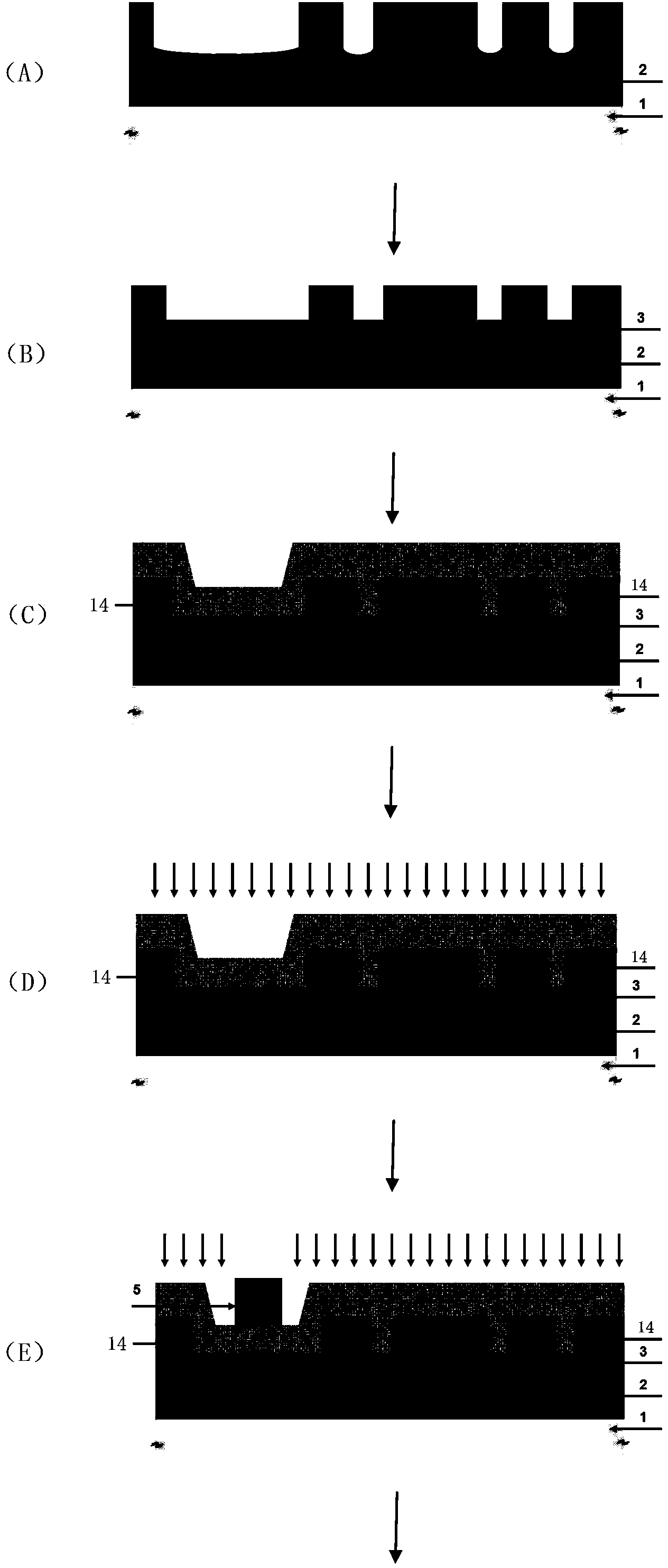

[0035] Step 1, grow an epitaxial layer 2 on the substrate 1, and then etch and form trenches on the epitaxial layer 2, such as image 3 (A) shown.

[0036] Step 2: Deposit a layer of dense silicon dioxide in the trench using atmospheric pressure chemical vapor deposition, and then etch back to form a 3000-4000 angstrom thick gate oxide 3 at the bottom of the trench, such as image 3 (B) shown. This layer of thick gate oxide 3 is used as an insulating layer between the electrostatic discharge prote...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com