A clock data recovery circuit and clock data recovery method

A clock data recovery and circuit technology, applied in the direction of electrical components, automatic power control, etc., can solve the problems of large clock jitter, long lock time, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

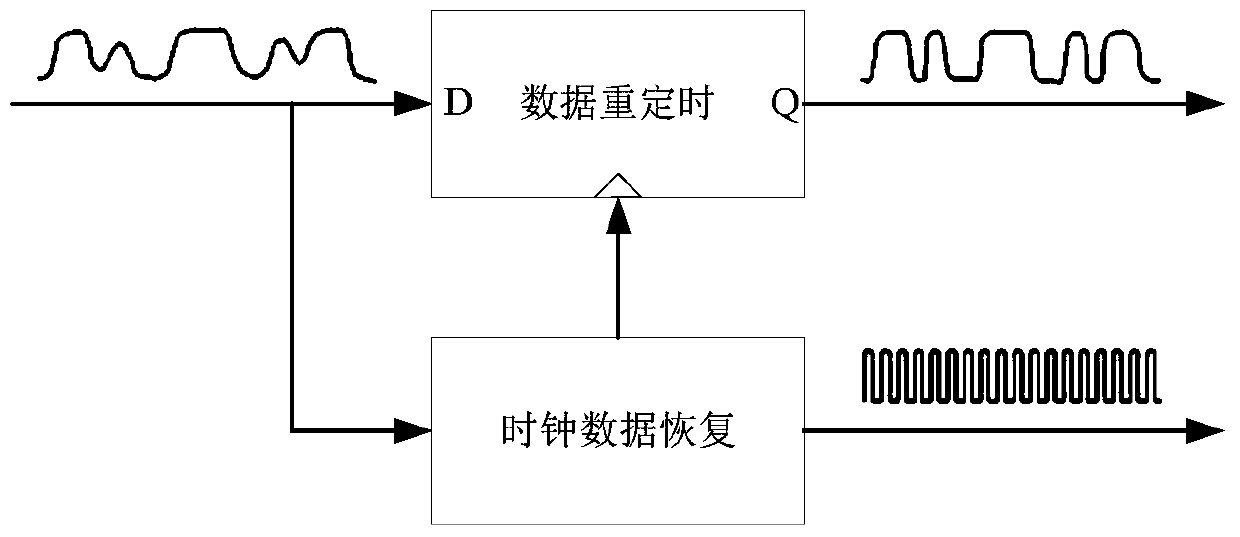

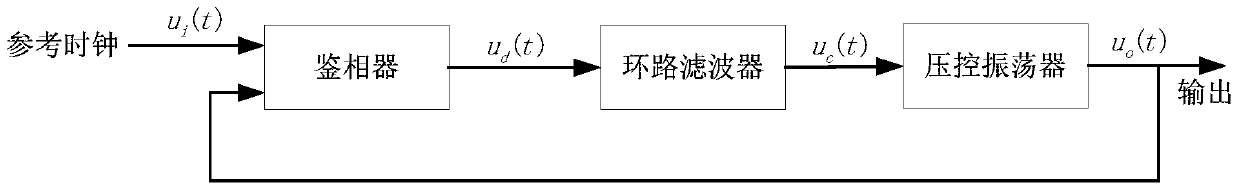

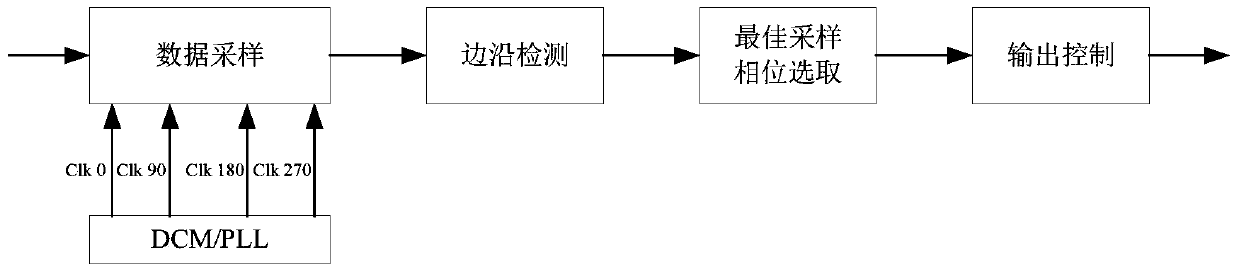

[0046] The core idea of the present invention is: aiming at the existing problems of the existing PLL-based clock data recovery circuit and the clock data recovery circuit based on the oversampling method, a kind of PLL-based oversampling method is provided. The all-digital clock data recovery circuit of FPGA (Field-Programmable Gate Array) is different from replacing every analog device in the traditional CDR circuit with a digital device. This clock data recovery circuit of the present invention is based on the digital correlation between input data Rather than simply sampling in the middle of the eye diagram, the recovered data is more stable and reliable. Moreover, how much the recovered clock phase shifts is determined by the finite state machine FSM (Finite State Machine), ensuring that the recovered clock signal is in phase with the recovered data. The clock data recovery circuit has the closed-loop characteristics of the phase-locked loop clock data recovery method, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More