A method for preparing a silicon carbide jfet gate structure with rectification

A gate structure, silicon carbide technology, used in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., to achieve the effect of expanding the working range, avoiding accidental opening, and improving channel conduction performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

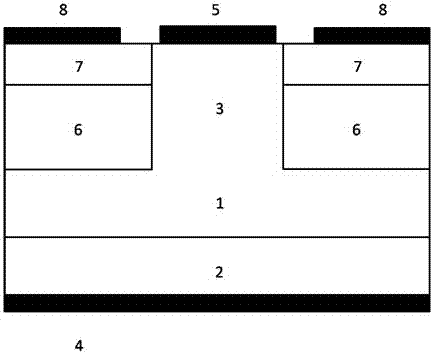

[0020] A method for preparing a silicon carbide JFET gate structure with a rectification function, comprising the following process steps:

[0021] 1) growing a first conductivity type layer 1 on a first conductivity type substrate 2;

[0022] 2) Two parts of the gate contact region 7 and the gate region 6 with the second conductivity type are respectively formed by two sets of implants, and the gate region 6 forms a PN junction with the drift region 1 and the channel region 3 with the first conductivity type;

[0023] 3) realizing ohmic contact between the source electrode 5 and the channel region 3 and between the drain electrode 4 and the substrate 2 of the first conductivity type by ohmic contact annealing;

[0024] 4) A rectifying gate contact is formed between the gate electrode 8 and the gate contact region 7 of the second conductivity type by rectifying gate contact annealing.

[0025] The turn-on voltage of the rectification grid can be controlled at 2V-20V.

[0026...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More