Superjunction device and manufacturing method

A super junction and device technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as device recovery current change, device failure, diode hard reverse recovery characteristics, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

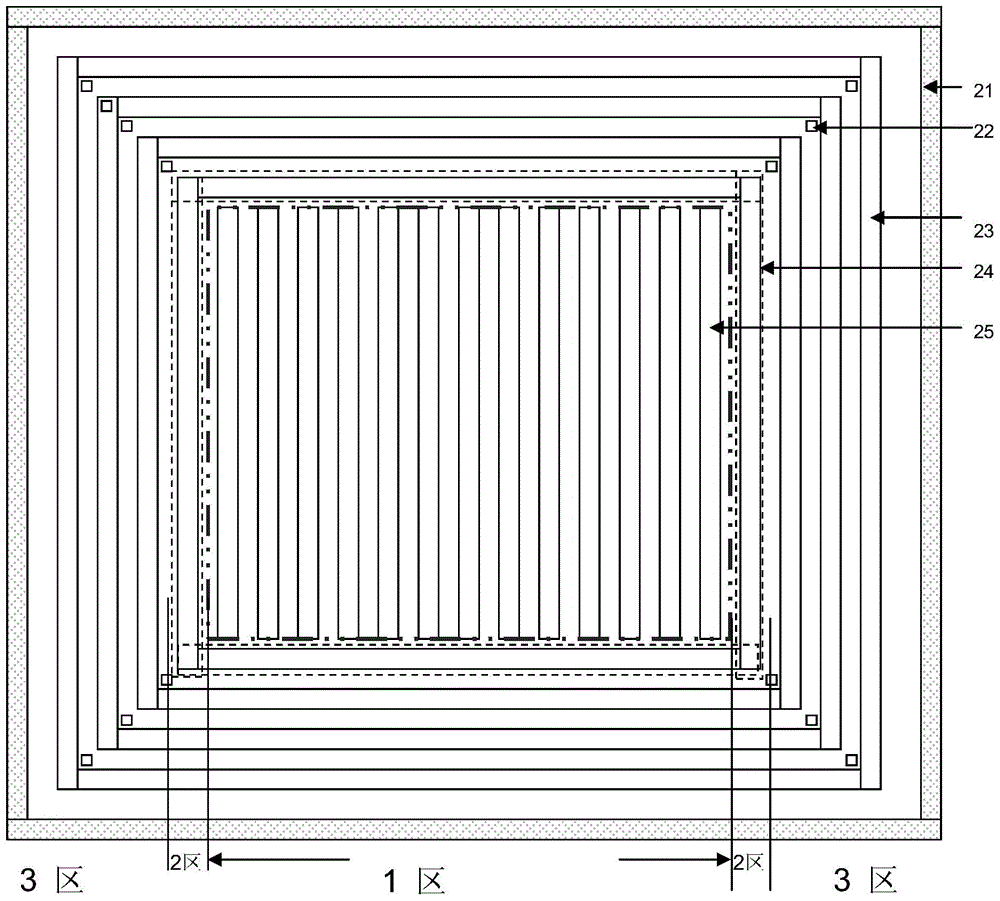

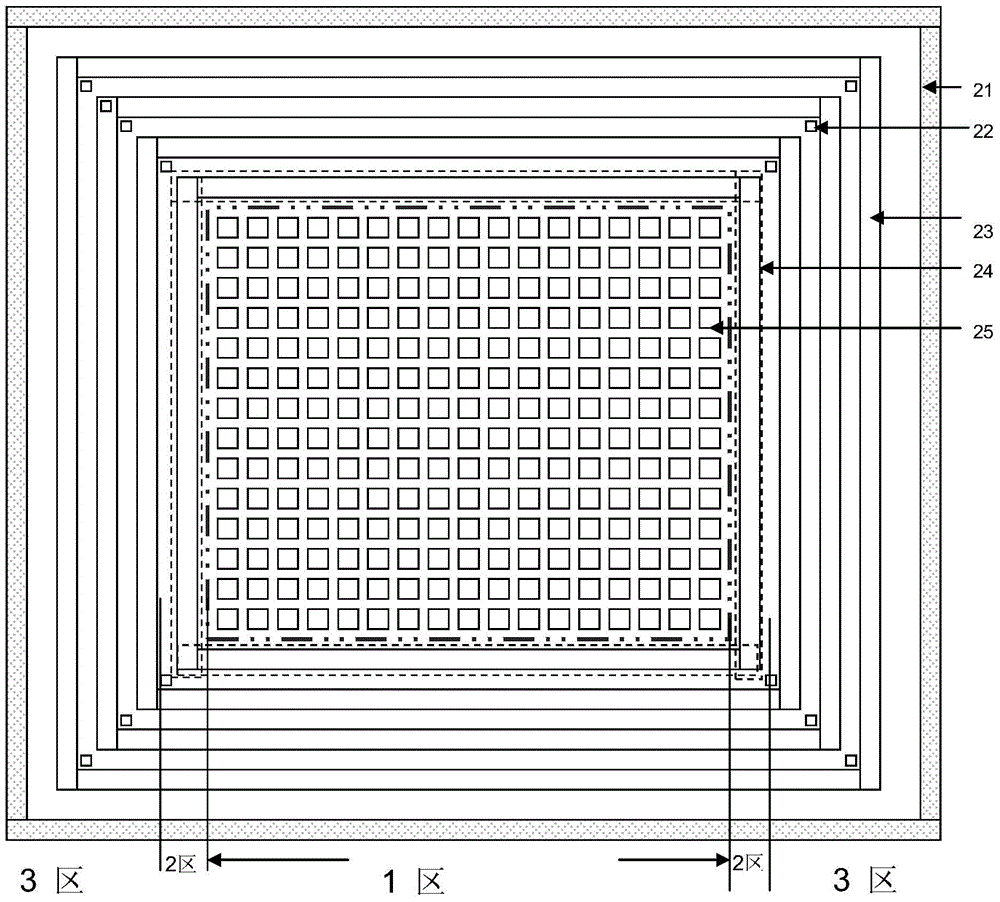

[0054] Such as figure 1 Shown is the top view of the existing super junction device Figure one . In the top view, the embodiment of the present invention can be divided into zone 1, zone 2, and zone 3. Region 1 is the middle region of the super junction device, which is the current flow region. The current flow region includes alternately arranged P-type regions 25 and N-type regions. The P-type region 25 is also the P-type region formed in the current flow region. The N-type thin layer, the N-type region is also the N-type thin layer formed in the current flow region; in the current flow region, the current will pass through the N-type region from the source to the drain through the channel, and the The P-type region 25 and the N-type region form a depletion region to withstand voltage in the reverse blocking state. Zone 2 and Zone 3 are the terminal protection structure area of the super junction device. When the device is turned on, the terminal protection structure does...

PUM

| Property | Measurement | Unit |

|---|---|---|

| electrical resistivity | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More