PMOS structure with SiGe source and drain area and manufacturing method thereof

A manufacturing method and technology for source and drain regions, which are applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of NiSi growth difficulties, stress relaxation, and device performance deterioration, and achieve enhanced device yield and improved device performance. stress, the effect of improving device performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

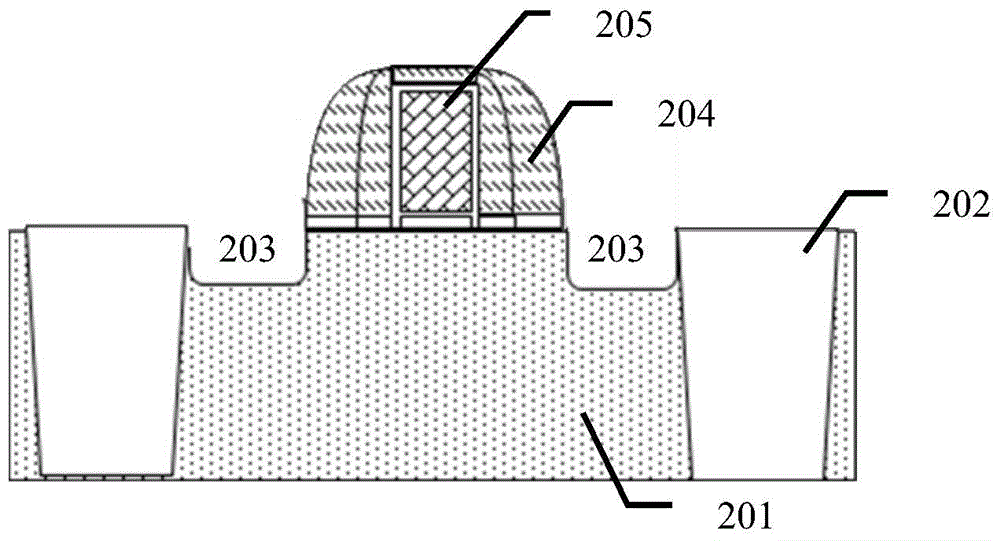

[0036] see Image 6 , the PMOS structure with SiGe source and drain regions in this embodiment includes a substrate 101, a gate 104 on the substrate 101, and source and drain regions on both sides of the gate 104 and between the shallow trench isolation 102, the source and drain regions Manufactured in the etched groove 103, the source and drain regions sequentially include a SiGe buffer layer 105, a SiGe body layer 106, and a Si cap layer 107 from bottom to top, wherein the SiGe body layer includes a first body layer from bottom to top and the second body layer, the Ge concentration of the first body layer increases from bottom to top, and the Ge concentration of the second body layer decreases from bottom to top, and the highest Ge concentration of the two is the same.

[0037] In this embodiment, through the above-mentioned settings, the first main body layer with increasing Ge concentration and the second main body layer with decreasing Ge concentration are arranged in the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More