Rapid reliability evaluation method for SRAM (Static Random Access Memory) type FPGA (Field Programmable Gate Array)

A reliable and fast technology, applied in the field of reliability evaluation of SRAM-type FPGAs and fast reliability evaluation of SRAM-type FPGAs, can solve the problems of long calculation time and insufficient calculation accuracy, and achieve reduced calculation time, high calculation accuracy, Overcome long computation time effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

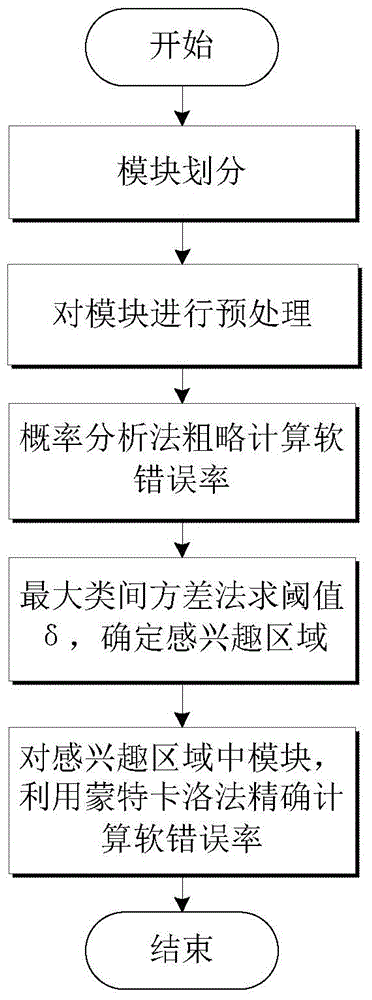

[0052] The present invention will be described in further detail below with reference to the accompanying drawings.

[0053] Reference figure 1 The specific implementation steps of the present invention are as follows:

[0054] Step 1: Determine the module division criteria according to the design rules of the VHDL hardware language. Read the source file of the VHD project, divide the modules according to the module division criteria, and obtain the independent and comprehensively mapable VHD files of L modules. The value of L depends on the scale and design structure of the VHD project source program. The module division criteria are as follows:

[0055] (1) If the VHDL code is a process statement (process), it will be regarded as a module;

[0056] (2) If the segment of VHDL code is a component instantiation statement, it will be regarded as a module, where the component instantiation statement represents the statement used to connect the underlying module and build the upper modu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More