Storage method of sparse matrix on SIMD multi-core processor with multi-level cache

A technology of many-core processors and sparse matrices, applied in the field of parallel programming, can solve the problems of low x-vector data reuse rate, low SIMD utilization rate, missing cache and high memory access delay overhead, etc., to improve utilization rate, The effect of high density and improved computing efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

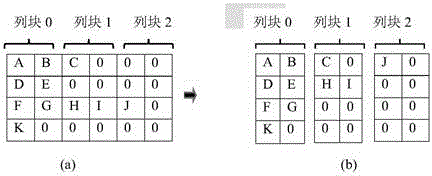

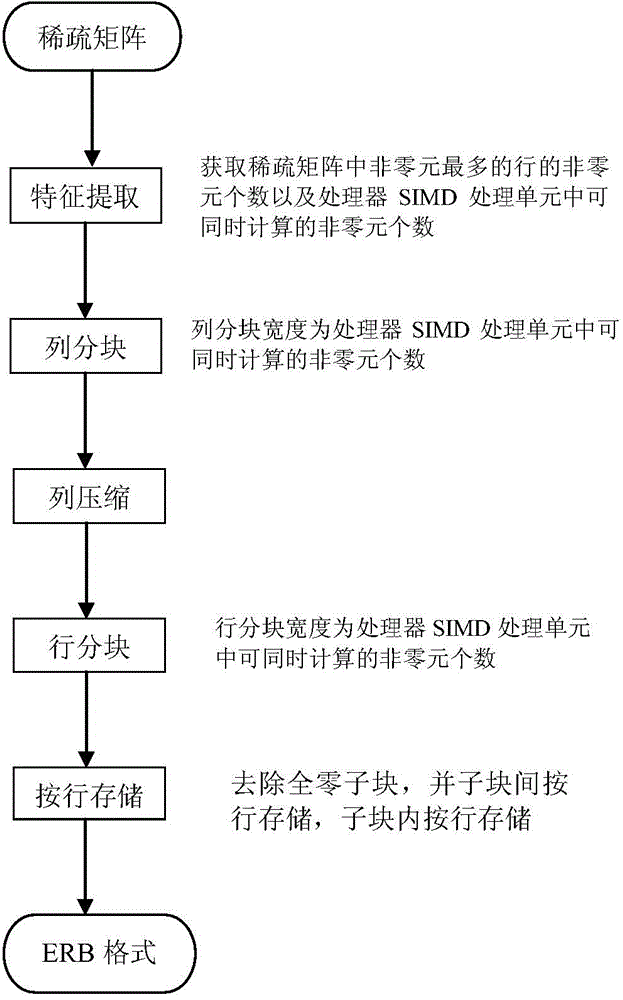

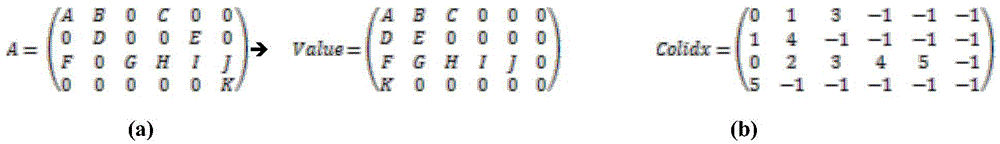

[0027] This section applies the present invention to a typical sparse matrix-vector multiplication calculation on a SIMD many-core processor with multi-level Cache. Thereby, the object, advantages and key technical features of the present invention are further described. This implementation is only a typical example of the solution, and any technical solution formed by replacement or equivalent transformation falls within the scope of protection claimed by the present invention.

[0028] For a sparse matrix A to be computed:

[0029] A = A B 0 C 0 0 0 D 0 0 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More